Sommario:

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:01.

- Ultima modifica 2025-01-23 14:49.

Collega la tua scheda di sviluppo Mojo a ingressi esterni con questo shield.

Che cos'è la scheda di sviluppo Mojo?

La scheda di sviluppo Mojo è una scheda di sviluppo basata sull'FPGA spartan 3 di Xilinx. La tavola è fatta da Alchitry. Gli FPGA sono molto utili quando più processi devono essere eseguiti contemporaneamente.

Di cosa avrai bisogno?

Forniture

Scheda di sviluppo Mojo

File Gerber

8 resistenze da 15k ohm (opzionali*)

4 x 470 ohm resistori

4 x 560 ohm resistori

4 display CC a sette segmenti

4 LED da 3 mm

4 x interruttori tattili SPDT

1 x 4 posizioni DIP switch per montaggio su superficie

Intestazioni 2 x 25 per 2 o 4 x 25

1x testa della scatola da 2 a 5 pin

Saldatore

Saldare

Flusso

*(se queste resistenze vengono omesse, il pullup/pulldown interno deve essere abilitato per i relativi pin)

Passaggio 1: carica Gerber sul produttore di PCB di tua scelta

Per le mie schede ho ordinato da JLC PCB.

L'unico cambiamento che ho fatto è stato il colore che volevo abbinare al nero del Mojo.

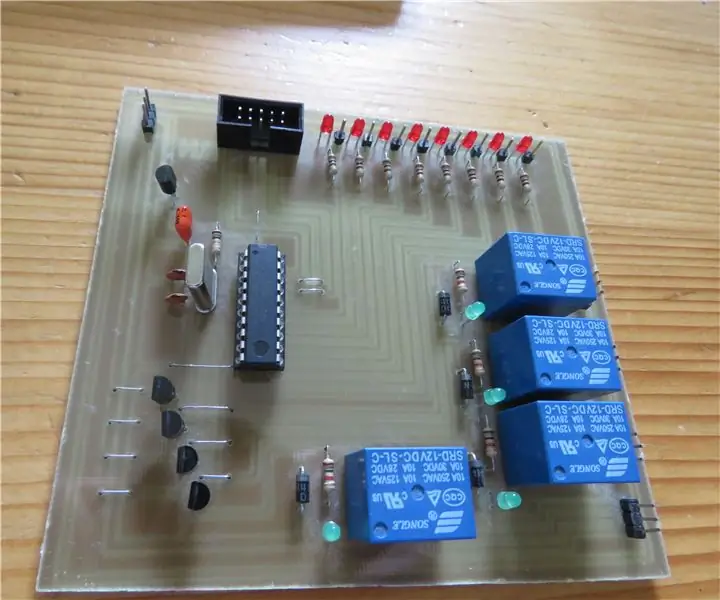

Passaggio 2: Assemblea del consiglio di amministrazione

Quando si salda, trovo sempre utile saldare prima le parti più basse, quindi iniziare con i resistori è una buona idea.

R5, R6, R7, R8, R9, R10, R11 e R12 sono resistori da 15k ohm usati per abbassare gli interruttori (se stai usando pullup/pulldown interni ignoralo).

R1, R2, R3, R4 sono resistori da 560 ohm responsabili della limitazione della corrente attraverso il display a 7 segmenti.

R13, R14, R15, R16 sono resistori da 470 ohm che sono responsabili della limitazione della corrente attraverso i 4 LED.

Quindi saldare il dip switch, gli interruttori tattili, i LED, i display a sette segmenti e il connettore dell'intestazione della scatola in questo ordine.

Ora posiziona il 25 per 2 (o 2 25 per 1) nel mojo per allineare i perni. Allineare lo scudo con i perni e saldarlo in posizione.

Passaggio 3: installazione del software

Per il software, fare riferimento al sito Web di Alchitry che ti consentirà di sapere di cosa hai bisogno per iniziare e installare Xilinx ISE. Tuttavia, cambiando il file.ucf in modo che sappia a quali pin sono collegati ciò che è importante per far funzionare il tuo programma.

Ecco il file.ucf che uso con lo scudo:

CONFIG VCCAUX=3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIODO "clk" 50 MHz ALTO 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "primo_n" LOC = P38 | IOSTANDARD = LVTTL; NETTO "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NETTO "Q[0]" LOC = P26 | IOSTANDARD = LVTTL; NETTO "Q[1]" LOC = P23 | IOSTANDARD = LVTTL; NETTO "Q[2]" LOC = P21 | IOSTANDARD = LVTTL; NETTO "Q[3]" LOC = P16 | IOSTANDARD = LVTTL; NETTO "S[0]" LOC = P7 | IOSTANDARD = LVTTL; NETTO "S[1]" LOC = P9 | IOSTANDARD = LVTTL; NETTO "S[2]" LOC = P11 | IOSTANDARD = LVTTL; NETTO "S[3]" LOC = P14 | IOSTANDARD = LVTTL; NETTO "pb[1]" LOC = P30 | IOSTANDARD = LVTTL; NETTO "pb[2]" LOC = P27 | IOSTANDARD = LVTTL; NETTO "pb[3]" LOC = P24 | IOSTANDARD = LVTTL; NETTO "pb[4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega[0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb[0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc[0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd[0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege[0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf[0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg[0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp[0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega[1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb[1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc[1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd[1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege[1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf[1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg[1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp[1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega[2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb[2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc[2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd[2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege[2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf[2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg[2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp[2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega[3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb[3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc[3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd[3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege[3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf[3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg[3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp[3]" LOC = P121 | IOSTANDARD = LVTTL;

Ricorda se non hai installato i resistori pulldown per modificare i pin nel.ucf con

| TIRARE; o

| PULLUP;

Se vuoi usare il blocco per qualsiasi cosa, le connessioni sono le seguenti. A sinistra è il numero pin del blocco ea destra è il numero pin mojo che dovresti assegnare nel tuo.ucf:

pin 1 = 29

pin 2 = 51

pin 3 = 32

pin 4 = 41

pin 5 = 34

pin 6 = 35

pin 7 = 40

pin 8 = 33

pin 9 = GND

pin 10 = +V

Consigliato:

Sviluppo della scheda Drivemall: 5 passaggi

Sviluppo della scheda Drivemall: In questo tutorial vedremo i passaggi fondamentali per creare una scheda Arduino personalizzata. I software utilizzati sono KiCad per la progettazione della scheda e l'IDE Arduino per la creazione e il caricamento del firmware per la scheda

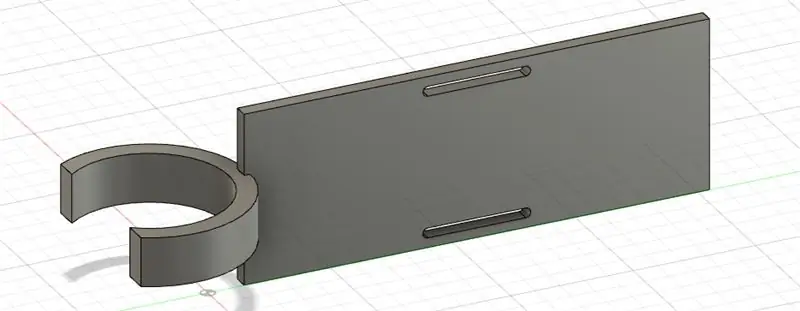

Vocal GOBO - Scudo smorzatore del suono - Cabina vocale - Box vocale - Filtro di riflessione - Scudo vocale: 11 passaggi

Vocal GOBO - Sound Dampener Shield - Vocal Booth - Vocal Box - Reflexion Filter - Vocalshield: ho iniziato a registrare più voci nel mio home studio e volevo ottenere un suono migliore e dopo alcune ricerche ho scoperto che cosa è un "GOBO" era. Avevo visto queste cose che smorzano il suono, ma non mi rendevo davvero conto di cosa facessero. Ora faccio. ho trovato un y

Scheda di sviluppo ESP32 fai da te - ESPer: 5 passaggi (con immagini)

Scheda di sviluppo ESP32 fai-da-te - ESPer: Di recente ho letto di molti IoT (Internet of Things) e fidati di me, non vedevo l'ora di testare uno di questi meravigliosi dispositivi, con la possibilità di connettersi a Internet, me stesso e mettere le mani sul lavoro. Per fortuna l'occasione a

Crea la tua scheda di sviluppo con microcontrollore: 3 passaggi (con immagini)

Crea la tua scheda di sviluppo con microcontrollore: hai mai desiderato creare la tua scheda di sviluppo con microcontrollore e non sapevi come. In questo tutorial ti mostrerò come realizzarla. Tutto ciò di cui hai bisogno è conoscenza dell'elettronica, progettazione di circuiti e programmazione. Se hai qualche missione

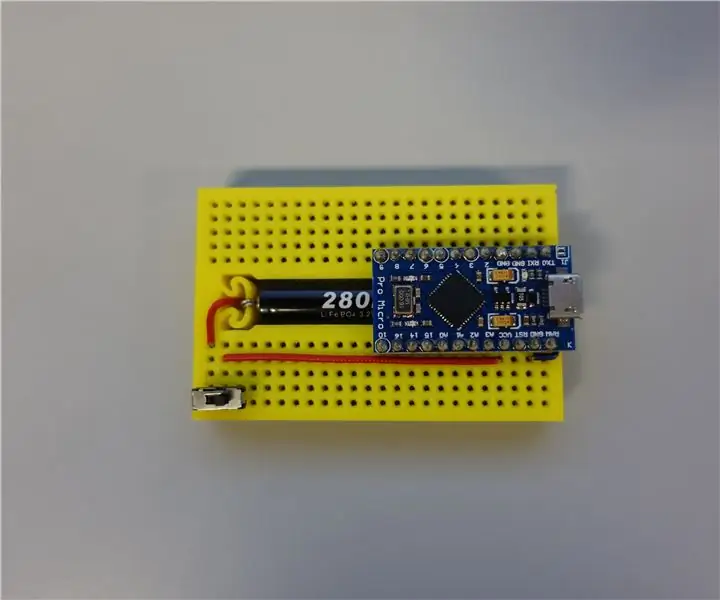

Breadboard della scheda di sviluppo: 12 passaggi (con immagini)

Breadboard della scheda di sviluppo: questo Instructables mostra come creare una breadboard su misura per la scheda di sviluppo