Sommario:

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:02.

- Ultima modifica 2025-01-23 14:49.

Sono sopraffatto dal tipo di risposte che ricevo in questo blog. Grazie ragazzi per aver visitato il mio blog e avermi motivato a condividere le mie conoscenze con voi. Questa volta presenterò il design di un altro modulo interessante che vediamo in tutti i SOC: Interrupt Controller.

Progetteremo un controller di interrupt programmabile semplice ma potente. È un design completamente configurabile e parametrizzato che è portabile su più piattaforme. L'ho progettato dopo aver letto molto su alcune architetture di controller di interrupt popolari là fuori come NVIC, 8259a, RISC-V PLIC, INTC di Microblaze ecc. Spero che voi ragazzi troviate questo blog utile e vi aiuti a capire come gli interrupt sono gestiti da un processore con l'aiuto di un Interrupt Controller.

Passaggio 1: specifiche

Di seguito le specifiche dell'IP:

- Interfaccia AHB3-Lite.

-

Parametri staticamente configurabili:

- N. di sorgenti di interrupt esterne; supporta fino a 63 interrupt.

- N. di livelli di priorità; supporta fino a 63 livelli.

- N. di livelli di nidificazione; supporta fino a 8 livelli di nidificazione.

- Larghezza del bus; 32 o 64.

- Interrupt mascherabili a livello globale e locale.

- Livello di priorità configurabile dinamicamente per ogni interrupt.

- Due modalità di funzionamento: modalità completamente annidata e modalità a priorità uguale.

- Supporta interrupt sensibili attivi di alto livello.

Nella progettazione viene utilizzato un meccanismo di handshake di interruzione ispirato alle specifiche RISC-V PLIC.

La prelazione di interruzione si ispira a 8259a

Altre letture: Microblaze INTC, NVIC

Passaggio 2: panoramica di PIC

Programmable Interrupt Controller (PIC) riceve più interrupt da periferiche esterne e li unisce in un unico output di interrupt a un core del processore di destinazione.

Il PIC è controllato tramite registri di controllo e di stato. Tutti i registri PIC sono mappati in memoria e vi si accede tramite l'interfaccia bus AHB3-Lite.

Il banco di registri è costituito da registro di configurazione, registri di abilitazione, registri in sospeso, registri in servizio, registri di priorità e registro ID, che sono tipici nei controller di interrupt.

Il registro di configurazione viene utilizzato per impostare la modalità di funzionamento del PIC. Può funzionare sia in modalità completamente annidata che in modalità priorità uguale.

Ad ogni interrupt possono essere assegnate priorità e mascherate individualmente. È supportato anche il mascheramento globale di tutti gli interrupt.

La banca del registro interagisce con Priority Resolver e BTC (Binary-Tree-Comparator) per risolvere le priorità degli interrupt in sospeso e asserire l'interruzione al processore di conseguenza. Il registro ID contiene l'ID dell'interruzione in sospeso con la priorità più alta.

Passaggio 3: progettazione e implementazione RTL

Lo sforzo di progettazione di PIC sulla riduzione della latenza della risoluzione delle priorità, che è la parte più critica in termini di tempo del progetto. Poiché il design risolve le priorità in un singolo ciclo di clock, le prestazioni peggiorano con l'aumento del numero di sorgenti con complessità Log2.

Il progetto è stato implementato con successo e la tempistica è stata verificata fino alle seguenti frequenze sugli FPGA Artix-7.

- Fino a 15 sorgenti: 100 MHz

- Fino a 63 sorgenti: 50 MHz

La latenza di interrupt aggiunta dal solo PIC è di 3 cicli di clock (escludendo il tempo di commutazione del contesto del processore e il tempo di recupero della prima istruzione ISR).

Passaggio 4: note importanti e file allegati

Note importanti:

- Se l'interfaccia AHB3-Lite non è desiderata, è possibile modificare il modulo superiore e utilizzare il design dello scheletro di PIC. Tuttavia il banco di prova fornito è per IP con interfaccia AHB3-Lite.

- PIC IP v1.0 è un design RTL nudo e completamente portatile.

- Funzionalmente verificato per funzionare su entrambe le modalità.

Files allegati:

- Codici di progettazione e banco di prova in VHDL.

- Documentazione IP completa.

È un design open source … Sentiti libero di usare …

Per qualsiasi domanda, in qualsiasi momento:

Mitu Raj

Consigliato:

Progettazione di un semplice controller di cache associativa a quattro vie in VHDL: 4 passaggi

Progettazione di un semplice controller di cache associativo a quattro vie in VHDL: nel mio precedente tutorial, abbiamo visto come progettare un semplice controller di cache a mappatura diretta. Questa volta facciamo un passo avanti. Progetteremo un semplice controller di cache associativo a quattro vie. vantaggio? Meno miss rate, ma a scapito delle prestazioni

Progettazione di un semplice controller di cache in VHDL: 4 passaggi

Progettazione di un controller di cache semplice in VHDL: Sto scrivendo questo istruibile, perché ho trovato un po' difficile ottenere del codice VHDL di riferimento per imparare e iniziare a progettare un controller di cache. Quindi ho progettato da zero un controller della cache e l'ho testato con successo su FPGA. ho p

Progettazione del Master I2C in VHDL: 5 passaggi

Progettazione di I2C Master in VHDL: in questo tutorial, viene discussa la progettazione di un semplice master I2C in VHDL. NOTA: fare clic su ciascuna immagine per visualizzare l'immagine completa

Progettazione di un semplice controller VGA in VHDL e Verilog: 5 passaggi

Progettazione di un semplice controller VGA in VHDL e Verilog: in questo tutorial, progetteremo un semplice controller VGA in RTL. VGA Controller è il circuito digitale progettato per pilotare i display VGA. Legge dal Frame Buffer (VGA Memory) che rappresenta il frame da visualizzare e genera neces

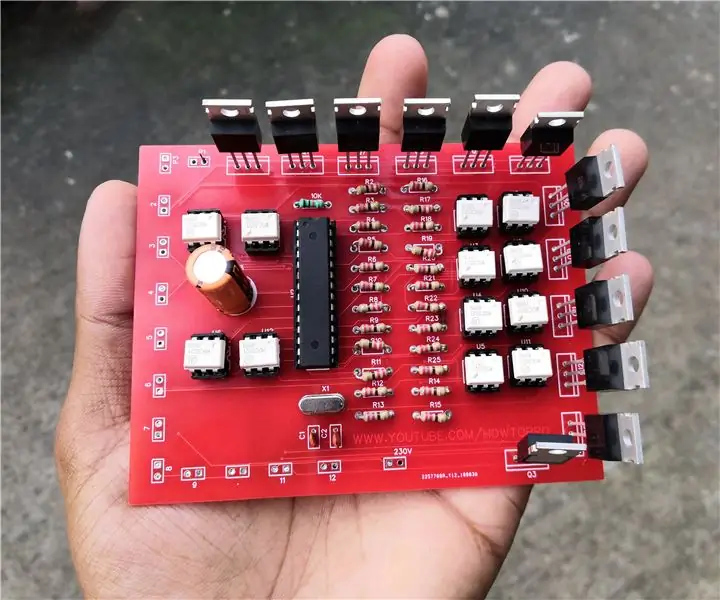

Fai da te Massiccio 12000 Watt 230 V Programmabile Illuminazione Programmabile 12 Canali: 10 Passi

Configurazione dell'illuminazione programmabile a 12 canali da 12000 Watt e 230 V fai-da-te: Ciao a tutti, in questo progetto ti mostrerò come creare un enorme controller di luci a led da 12000 watt. Questa è una configurazione a 12 canali, utilizzando questo circuito puoi controllare qualsiasi luce da 230 V .Puoi creare diversi modelli di illuminazione. In questo video ho