Sommario:

- Forniture

- Passaggio 1: requisiti della porta seriale

- Fase 2: Requisiti di programmazione PIC

- Passaggio 3: specifica JDM

- Passaggio 4: descrizione del circuito

- Passaggio 5: prepararsi per la simulazione

- Passaggio 6: modifiche per ICSP

- Passaggio 7: risultati della simulazione

- Passaggio 8: Conclusioni

- Passaggio 9: e infine

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 09:59.

- Ultima modifica 2025-01-23 14:49.

JDM è un popolare programmatore PIC perché utilizza una porta seriale, un minimo di componenti e non richiede alimentazione. Ma c'è confusione là fuori, con molte varianti del programmatore in rete, quali funzionano con quali PIC? In questo "istruttivo" mettiamo alla prova JDM e dimostro come simulare il circuito usando Spice che risponderà a tutte le tue domande!

Forniture

LTspice che può essere scaricato da Analog Devices qui.

Hai anche bisogno dei file del circuito JDM qui.

Passaggio 1: requisiti della porta seriale

JDM richiede una porta seriale che soddisfi le specifiche EIA232, idealmente con livelli di tensione +12/-12.

Secondo la scheda tecnica Texas Instruments Line Driver MC1488 (Figura 3)

Impedenza di uscita = 4V/8mA = 500 ohm.

Limite di corrente di cortocircuito = 12 mV, senza limiti di tempo - nessun danno al chip.

Impedenza di ingresso del ricevitore di linea = consigliata da 3k a 7k ohm.

Le porte seriali sui vecchi PC desktop utilizzano +12v/-12V per soddisfare questo requisito.

Le porte seriali sui PC portatili più recenti utilizzano voltaggi più bassi. JDM può o non può funzionare: la risposta è più complessa.

Fase 2: Requisiti di programmazione PIC

Le informazioni relative ai requisiti di programmazione PIC sono ottenute da Microchip. Quanto sopra è per un dispositivo tipico.

Passaggio 3: specifica JDM

Il sito web originale di JDM si è perso nella notte dei tempi? Questo ci lascia indovinare cosa intendeva originariamente il progettista per la specifica.

- Fornire VDD=5V e fino a IDD=2mA massimo (per la versione “in socket”)

- Fornire VHH=13V e fino a IHH=0.2mA massimo.

- MCLR Tempo di salita tVHHR = 1uS max.

- La versione ICSP deve essere in grado di abbassare MCLR contro un pull-up di 22k sul bersaglio.

Passaggio 4: descrizione del circuito

La figura JDM1 è basata sul circuito JDM "standard" preso dal sito web PICPgm. Questo è il programmatore "PIC in Socket" in cui PIC prende l'alimentazione dai pin TX e RTS. Il diagramma originale era difficile da capire, quindi l'ho ridisegnato usando la normale convenzione del flusso di corrente dall'alto verso il basso. E ho aggiunto gli indicatori LED "RESET", "PROG" e "RTS" che sono necessari durante la costruzione e il test. Speriamo che questi non abbiano alcun effetto dannoso sul comportamento.

La normale convenzione della progettazione del circuito è quella di mettere in comune tutte le messe a terra, ma la caratteristica chiave di JDM è che la terra della porta seriale (GND) è collegata a VDD. Ciò crea confusione poiché i segnali della porta seriale vengono misurati rispetto a GND, i segnali PIC rispetto alla massa logica (VSS).

Quando TX diventa alto, Q1 si comporta come due diodi polarizzati in avanti. (Il collettore Q1 non è polarizzato inversamente come nel normale funzionamento del transistor). Il collettore Q1 carica C2, che è bloccato a VDD+8V da Zener (D3). L'emettitore Q1 fornisce 13V a MCLR per la modalità Program/Verify.

Quando TX si abbassa, il condensatore C3 viene caricato attraverso D1 e VSS viene bloccato a VDD-5V dallo zener (D5). Anche TX è bloccato a (VSS-0.6) da D1. Q1 è spento, C1 mantiene la sua carica per il prossimo impulso di programmazione. MCLR è bloccato a 0V da D2, quindi il PIC è ora ripristinato.

Quando RTS è alto, il clock viene trasmesso a PGC. D4 morsetto PGC a logica VDD alta. Quando l'RTS è basso, il condensatore C3 viene caricato tramite D6 e VSS viene bloccato a VDD-5V dallo zener (D5). D6 blocca PGC a VSS o logica 0.

Durante la programmazione, i dati inviati su DTR vengono letti su PGD, che il PIC configura come input. Quando DTR è alto, Q2 funge da "emettitore follower" e la tensione PGD è di circa (VDD-0.6) o logica 1. Quando DTR è basso, Q2 funge da transistor difettoso (pin emettitore e collettore invertiti). Q2 porta PGD basso, che è bloccato da D7 a VSS o logica 0.

Durante la verifica il PIC configura PGD come uscita per l'invio dei dati alla porta seriale. DTR deve essere impostato su alto e i dati vengono letti su CTS. Quando l'uscita PGD è alta, Q2 è spento, CTS = DTR = +12V. Quando l'uscita PGD è bassa, Q2 è attivo. Il collettore Q2 assorbe corrente (12V+5V)/(1k+1k5)=7mA da DTR e abbassa CTS a VSS.

Passaggio 5: prepararsi per la simulazione

Scarica LT spice, salva e apri i file del circuito (*.asc) forniti qui. Per simulare il circuito, dobbiamo dargli alcuni input, quindi "tracciare" le uscite. V1, V2 V3 simulano la porta seriale 12V con impedenza di uscita R11, R12, R13.

- V1 genera 2 impulsi di programma su TX da 0,5 ms a 4,5 ms

- V2 genera burst di impulsi di dati su DTR da 1,5 a 4,5 ms

- V3 genera burst di impulsi di clock su RTS da 0,5 a 3,5 ms

I componenti V4, X1, R15 e R16 fanno tutti parte della simulazione.

- V4 genera 2 impulsi da 2,5 a 4,5 ms per verificare i dati.

- Il jumper X1 simula l'USCITA su PGD.

- R15, R16 simulano il “caricamento” di PIC su VDD e MCLR.

Passaggio 6: modifiche per ICSP

La figura JDM3 mostra la versione per la programmazione “in circuit”. Le modifiche dall'originale sono

- Sostituire la presa ZIF con il connettore ICSP.

- Il PIC è ora alimentato dall'alimentazione al circuito di destinazione (V5).

- Rimuovere lo zener 5V (D5).

- Il piccolo condensatore da 100 pF (C4) viene spostato vicino al PIC sul circuito di destinazione.

- I LED prendono l'alimentazione dal circuito, ove possibile.

- Il resistore di pull-up MCLR (R10) e il diodo (D10) sono necessari sul circuito di destinazione.

- AVVERTIMENTO. La scheda target deve avere un'alimentazione "fluttuante", idealmente una batteria.

- Non collegare la massa target (VSS) alla terra del computer/PC collegando altre porte del computer contemporaneamente a JDM.

Dopo aver simulato JDM1, il problema del lungo tempo di carica su C2 è diventato evidente. Quindi, dopo aver letto Fruttenboel, sembra che C2 e Q1 siano stati aggiunti come modifica all'originale. Non riesco a pensare a cosa intendono fare C2 e Q1 oltre a creare problemi. Quindi, per JDM4, torniamo al vecchio design su Fruttenboel che è semplice e diretto da capire. D1 e D3/LED2 morsetto MCLR tra VSS e VDD+8V. Il valore di R1 si riduce a 3k3, quanto basta per illuminare il LED2 a 12V.

JDM4 è progettato anche per funzionare con porte seriali più deboli. Quando TX diventa alto (+9V), sorgente di corrente TX = (9-8)/(1k +3k3) = 0.2ma, quanto basta per portare MCLR alto anche se insufficiente per illuminare il LED2. Quando TX si abbassa (circa -7V), la corrente TX si abbassa =(9-7)/1k = 2mA. Corrente LED1 = (7-2 per led)/(2k7) = 1,8mA. Corrente di pull down MCLR = 7-5,5/3 k3 = 0,5 mA.

Questo circuito è stato anche testato (simulazione JDM5) per vedere cosa succede con le porte seriali +/-7V minimo, dove c'è una tensione insufficiente per sostenere VHH=13V. Lo scopo di C1 ora diventa evidente, C1 crea un breve +ve boost su MCLR, un picco di 33us sul fronte di salita di TX, sufficientemente lungo da consentire al PIC di entrare in modalità di programmazione, forse? Ma rimuovere il ponticello X2 (disabilita LED1) poiché non c'è corrente sufficiente per abbassare MCLR e illuminare LED1 insieme. Quando TX si abbassa, la corrente di TX si abbassa = (7V-5,5V)/(1k+3k3) = 0,3mA, appena sufficiente per abbassare MCLR contro il pull-up R10.

Passaggio 7: risultati della simulazione

Per visualizzare i file grafici, è meglio fare clic con il pulsante destro del mouse sui collegamenti sottostanti, quindi selezionare "Apri collegamento in una nuova scheda"

Simulazione 1: traccia di MCLR, VSS e RTS per JDM1 originale. Immediatamente l'osservazione 1, 2 e 3 sono evidenti.

Simulazione 2: traccia di MCLR e VSS e RTS per JDM2 modificato, che risolve i problemi precedenti.

Simulazione 3: traccia di PGD, VSS e PGC per JDM2 invio dati in modalità programma. Osservazione 4 a 3,5 mS.

Simulazione 4: traccia di PGD, VSS e CTS per JDM2 in modalità verifica (jumper X1 inserito). ok

Simulazione 5: traccia di MCLR, VSS, PGD e PGC per JDM3. L'ICSP che utilizza l'alimentazione dal circuito risolve molti problemi.

Simulazione 6: traccia di MCLR, VSS, PGD e PGC per JDM4 con porta seriale +/-9V. MCLR si alza subito, perfettamente funzionante.

Simulazione 7: traccia di MCLR, VSS e TX per JDM5 con porta seriale +/-7V e jumper X2 rimossi. C1 crea un +ve boost (spike) sul fronte di salita di MCLR, appena sufficiente per spingere MCLR sopra TX a 13V.

Passaggio 8: Conclusioni

Spice è davvero bravo a rivelare "segreti nascosti" del funzionamento del circuito. Evidentemente il circuito JDM funziona ed è compatibile con molti chip PIC, ma le seguenti osservazioni rivelano possibili limitazioni/problemi di compatibilità/difetti ?

- Tempo di salita lungo di MCLR mentre C2 si carica su VPP al primo impulso di TX. Non supera la specifica 3.

- La porta seriale carica C2 quando TX diventa alto e RTS diventa basso. Ma RTS ha anche il compito di caricare C3. Quando entrambi si verificano contemporaneamente, questo crea più carico su RTS, di conseguenza C3 perde carica (VSS aumenta) a 2 ms durante la simulazione. Non supera la specifica 1.

- C3 perde carica (VSS inizia a salire) dopo che gli impulsi di clock si fermano a 3,5 ms.

- Qual è lo scopo di C2, è necessario?

Soluzioni

- Presumibilmente PICPgm utilizza un software "work-round". Deve applicare un lungo impulso TX per precaricare su C2, quindi entrare in modalità programmazione solo dopo il secondo impulso TX? Per la simulazione ho ridotto il valore di C2 a 1uF per ottenere un tempo di salita di 1 ms. Non una soluzione ideale.

- Dividi C2 e C3 in modo che si carichino in modo indipendente. Una piccola modifica a JDM2, C2 fa riferimento a GND invece che a VSS.

- Risolto da JDM3. ICSP è molto più affidabile poiché il PIC è alimentato dal circuito di destinazione.

- JDM4 risolve il problema 1. Questo è un design semplice che elimina del tutto C2.

Passaggio 9: e infine

La prova del budino è nel mangiarlo. Questo JDM funziona, quindi continua a usarlo.

E i miei consigli sono:

- utilizzare JDM2 per la programmazione in socket e le porte seriali a 12V,

- usa JDM4 per programmatore ICSP e porte seriali sopra +/- 9V,

- utilizzare JDM4 con jumper X2 rimosso per porte seriali superiori a +/-7V.

Riferimenti:

Analog Devices LT spezia

picpgm

Fruttenboel

Segui altri progetti PIC su sly-corner

Consigliato:

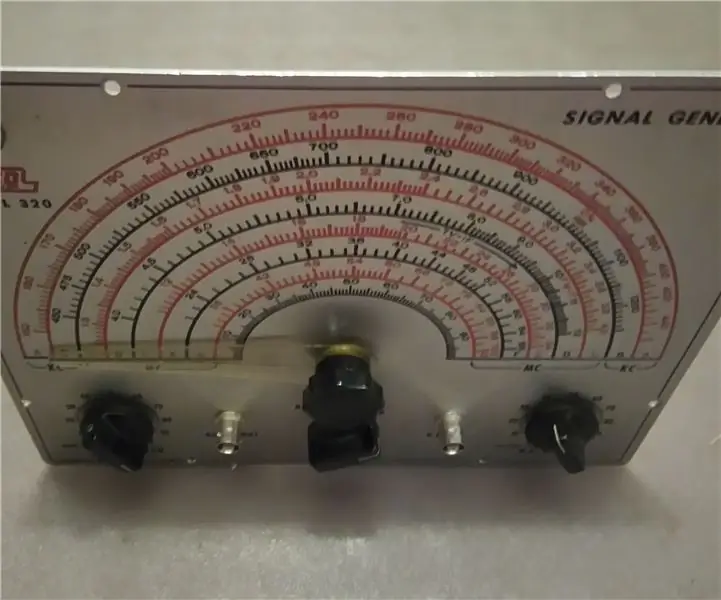

Revisione completa del generatore di segnale vintage: 8 passaggi

Revisione completa del generatore di segnale vintage: ho acquistato un generatore di segnale Eico 320 RF a un raduno di scambio di radioamatori per un paio di dollari alcuni anni fa, ma non sono mai riuscito a farci nulla fino ad ora. Questo generatore di segnale ha cinque gamme commutabili da 150 kHz a 36 MHz e con ha

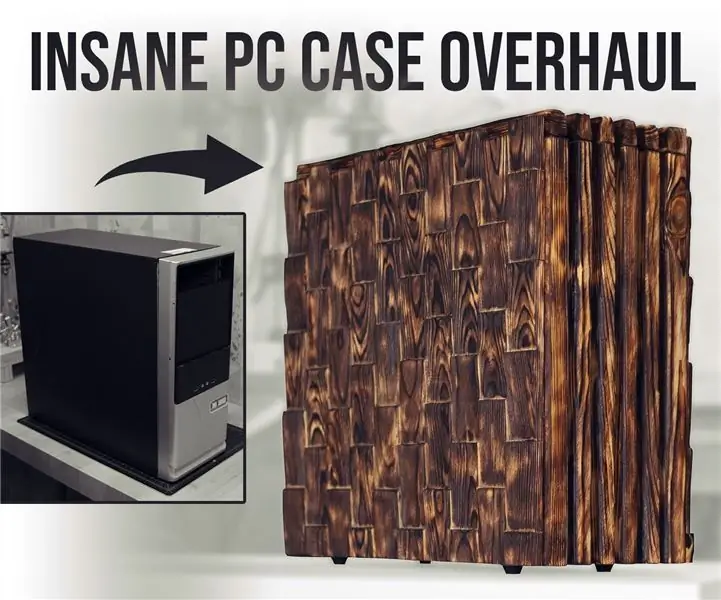

Revisione del case del PC folle: 23 passaggi (con immagini)

Insane PC Case Overhaul: In questo tutorial/video, farò una modifica relativamente semplice per ottenere un aspetto radicalmente diverso per un vecchio PC desktop. Ma non è solo per l'aspetto. Anche il flusso d'aria per i componenti interni sarà migliore. E questo permetterà p

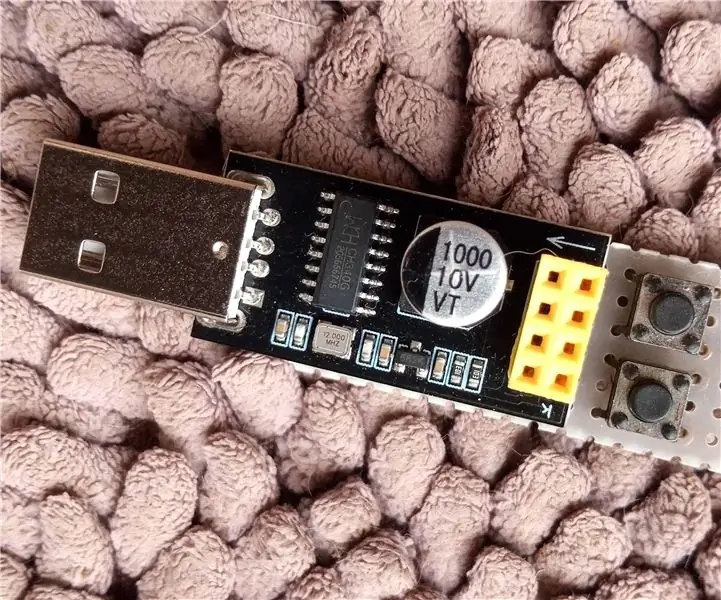

Hack del programmatore ESP-01 - quello facile :): 6 passaggi

ESP-01 Programmer Hack - the Easy One :): Ciao ESPers, in questo tutorial ti mostrerò un semplice trucco per creare un programmatore per il modulo ESP-01 / ESP8266-01 / ES-01. La maggior parte di noi ha utilizzato una scheda Arduino o dispositivi FTDI USB-TTL come programmatori per questo modulo. Entrambi i metodi funzionano bene. Ma t

Riparazione e revisione dell'otturatore Olympus Pen-EE: 16 passaggi

Riparazione e revisione dell'otturatore Olympus Pen-EE: la Olympus Pen-EE, del 1961 circa, può essere smontata con cura, pulita e revisionata e rimontata senza troppi rischi di perdere parti o danneggiare qualcosa all'interno - se sei pratico , costante e paziente, e hai lo strumento giusto

Acer Extensa Laptop 5620 Guida alla revisione di Hotrod: 12 passaggi

Acer Extensa Laptop 5620 Guida alla revisione di Hotrod: il nostro piccolo Acer Extensa 5620 è stato buono con noi negli ultimi due anni, eh? È una macchina abbastanza carina… ma… lo senti anche tu, vero? Funziona un po' lentamente, l'hard disk fa un po' di rumore, la batteria dura meno di venti minuti… è ora