Sommario:

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:00.

- Ultima modifica 2025-01-23 14:49.

Di AmCoderhttps://www.linkedin.com/in/mituFollow Altro dall'autore:

Informazioni su: Mitu Raj -- Solo un hobbysta e uno studente -- Progettista di chip -- Sviluppatore di software -- Appassionato di fisica e matematica Maggiori informazioni su AmCoder »

##Questo è il link più cliccato e popolare in Google per l'implementazione VHDL di CORDIC ALGORITHM per generare onde seno e coseno## Al momento, esistono molti algoritmi hardware efficienti, ma questi non sono ben noti a causa del predominio dei sistemi software su i molti anni. CORDIC è un algoritmo di questo tipo che non è altro che un insieme di logiche di spostamento e aggiunta utilizzate per calcolare un'ampia gamma di funzioni tra cui alcune funzioni trigonometriche, iperboliche, lineari e logaritmiche. Questo è l'algoritmo utilizzato nelle calcolatrici, ecc. Quindi, semplicemente usando semplici shifter e sommatori, possiamo progettare un hardware con meno complessità ma potenza del DSP utilizzando un algoritmo cordic. Quindi può essere progettato come design RTL nudo in VHDL o Verilog senza utilizzare unità in virgola mobile dedicate o IP matematici complessi.

Passaggio 1: VHDL e Modelsim

Qui l'algoritmo cordic è implementato usando VHDL per generare un'onda sinusoidale e un'onda cose. Può produrre seno e coseno dell'angolo di input con grande precisione. Il codice è sintetizzabile su FPGA. Modelsim viene utilizzato per simulare il progetto e il banco prova.

Passaggio 2: codice VHDL per la progettazione e il banco di prova

La tecnica di ridimensionamento binario viene utilizzata per rappresentare i numeri in virgola mobile.

Si prega di leggere i documenti allegati prima di codificare.

Vai alla simulazione cordic_v4.vhd - Il design - L'input è l'angolo in 32 bit + bit di segno; può elaborare qualsiasi angolo da 0 a +/- 360 gradi con una precisione di input di 0.000000000233 gradi. Quando si fornisce l'input -> MSB è il bit di segno e gli altri 32 bit rappresentano la grandezza.-L'output del progetto è il suo valore seno e cos in 16 bit + bit di segno.ie; con precisione 0.000001526. Si prega di notare che l'uscita viene visualizzata sotto forma di complimento a 2 se il rispettivo valore seno o cos è negativo. Simulazione di testb.vhd - Banco di prova per il progetto (1) Input angoli e pull reset ='0'. Dopo due passaggi di simulazione, resetta su '1' e "esegui tutto". (2) Nella finestra di simulazione imposta la radice dei segnali sin e cos come decimale e formato > Analogico (automatico). (3) Rimpicciolisci per vedere la forma d'onda propriamente.

Passaggio 3: file allegati

(1) cordic_v4.vhd - Progettazione.(2) testb.vhd - Banco prova per la progettazione.

(3) Documento su come forzare gli input angolari e convertire i risultati binari.

Aggiornamento: QUESTI FILE SONO OBSELETE E NON PIU' FORNITI. SI PREGA DI UTILIZZARE I FILE DEL PASSO SUCCESSIVO

Passaggio 4: Mini-Cordic IP Core - 16 Bit

La limitazione dell'implementazione di cui sopra è la frequenza di funzionamento lenta e di clock inferiore a causa dell'esecuzione di calcoli in un singolo ciclo di clock. Mini-Cordic IP Core - 16 Bit

- Percorsi critici distribuiti su più cicli per migliorare le prestazioni.- Più veloce - Design collaudato FPGA sintetizzato fino a 100 Mhz di clock.- Più area ottimizzata in HDL, hardware minore.- Aggiunti segnali di stato di carico e di fine.- L'unico aspetto negativo è la risoluzione inferiore rispetto al precedente. Banco di prova:

completamente automatizzato da 0 a 360 gradi ingressi angolari

File allegati: 1) mini cordic main vhdl file2) mini cordic test bench3) mini cordic IP Core manuale4) documento su come forzare gli angoli e convertire i risultati

Per qualsiasi domanda non esitare a contattarmi:

Mitu Raj

seguimi:

mail: iammituraj@gmail.com

###Download totali: 325 fino al 01-05-2021###

### Ultima modifica del codice: 07-luglio-2020 ###

Consigliato:

Robot di autobilanciamento - Algoritmo di controllo PID: 3 passaggi

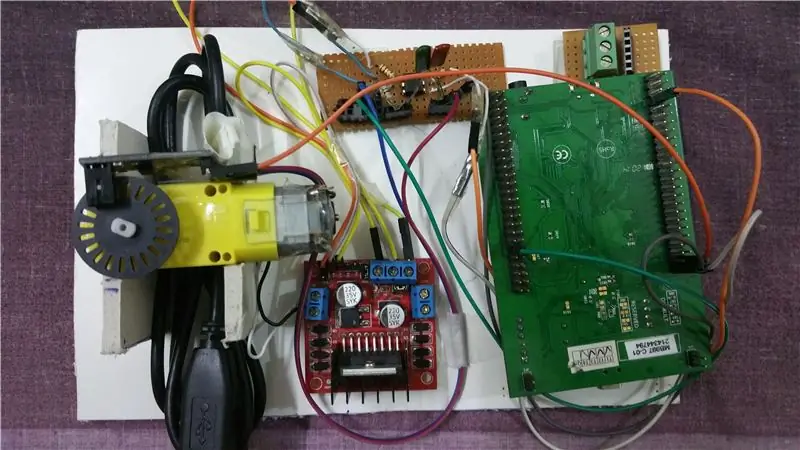

Self Balancing Robot - Algoritmo di controllo PID: questo progetto è stato concepito perché ero interessato a saperne di più sugli algoritmi di controllo e su come implementare in modo efficace i loop PID funzionali. Il progetto è ancora in fase di sviluppo in quanto deve ancora essere aggiunto un modulo Bluetooth che sarà al

Gioco da tavolo Intelligenza artificiale: l'algoritmo Minimax: 8 passaggi

Gioco da tavolo Intelligenza artificiale: l'algoritmo Minimax: ti sei mai chiesto come sono fatti i computer contro cui giochi a scacchi oa dama? Bene, non guardare oltre questo Instructable perché ti mostrerà come creare un'intelligenza artificiale (AI) semplice ma efficace usando l'algoritmo Minimax! Usando il

Robot di autobilanciamento che utilizza l'algoritmo PID (STM MC): 9 passaggi

Robot di autobilanciamento che utilizza l'algoritmo PID (STM MC): Recentemente è stato fatto molto lavoro nell'autobilanciamento degli oggetti. Il concetto di autobilanciamento è iniziato con il bilanciamento del pendolo invertito. Questo concetto si estese anche alla progettazione di velivoli. In questo progetto, abbiamo progettato un piccolo mod

Tic Tac Toe su Arduino con AI (algoritmo Minimax): 3 passaggi

Tic Tac Toe su Arduino With AI (Minimax Algorithm): in questo Instructable ti mostrerò come costruire un gioco Tic Tac Toe con un'intelligenza artificiale usando un Arduino. Puoi giocare contro Arduino o guardare Arduino giocare contro se stesso. Sto usando un algoritmo chiamato "algoritmo minimox"

Controllo della velocità del motore CC utilizzando l'algoritmo PID (STM32F4): 8 passaggi (con immagini)

Controllo della velocità del motore CC utilizzando l'algoritmo PID (STM32F4): ciao a tutti, questo è tahir ul haq con un altro progetto. Questa volta è STM32F407 come MC. Questo è un progetto di fine semestre. Spero ti piaccia. Richiede molti concetti e teoria, quindi ci occupiamo prima di tutto. Con l'avvento dei computer e del