Sommario:

- Passaggio 1: creazione di un modulo PWM - File sorgente

- Passaggio 2: creazione di un modulo PWM - Configurazione Vivado

- Passaggio 3: creazione di un modulo PWM: creazione di un file di progetto

- Passaggio 4: creazione di un modulo PWM: progettazione del blocco e impostazione del file di vincoli (I)

- Passaggio 5: creazione di un modulo PWM: progettazione del blocco e impostazione del file di vincoli (II)

- Passaggio 6: creazione di un modulo PWM: progettazione del blocco e impostazione del file di vincoli (III)

- Passaggio 7: creazione di un modulo PWM: progettazione del blocco e impostazione del file di vincoli (IV)

- Passaggio 8: creazione di un modulo PWM: progettazione del blocco e impostazione del file di vincoli (V)

- Passaggio 9: creazione di un modulo PWM - Installazione hardware

- Passaggio 10: creazione di un modulo PWM: generazione di bitstream e avvio dell'SDK

- Passaggio 11: creazione di un modulo PWM: creazione di una nuova applicazione in Xilinx SDK

- Passaggio 12: creazione di un modulo PWM - Panoramica di Project Explorer (I)

- Passaggio 13: creazione di un modulo PWM - Panoramica di Project Explorer (II)

- Passaggio 14: creazione di un modulo PWM - Panoramica di Project Explorer (III)

- Passaggio 15: creazione di un modulo PWM: conclusione della funzione PWM (I)

- Passaggio 16: creazione di un modulo PWM - Riepilogo della funzione PWM (II)

- Passaggio 17: creazione di un modulo PWM - Riepilogo della funzione PWM (III)

- Passaggio 18: creazione di un modulo PWM: fallo funzionare

- Passaggio 19: elaborazione video in streaming su Digilent ZYBO con OV7670

- Passaggio 20: diagramma a blocchi completo

- Passaggio 21: collegare l'OV7670 a ZYBO

- Passaggio 22: creare un design a blocchi

- Passaggio 23: aggiungere file VHDL per il controllo e l'acquisizione della fotocamera OV7670

- Passaggio 24: aggiungere il file dei vincoli

- Passaggio 25: aggiungere repository IP per IP HLS

- Passaggio 26: aggiungere moduli e IP

- Passaggio 27: impostazioni di configurazione IP

- Passaggio 28: aggiungere e configurare il blocco IP di PS

- Passo 29: Parte 1. Costruire un modulo PWM per servomotori

- Passaggio 30: connessioni lato ingresso video (evidenziato con aclk)

- Passaggio 31: connessioni a OV7670

- Passaggio 32: connessioni sul lato uscita video

- Passaggio 33: eseguire blocco e automazione della connessione

- Passaggio 34: Genera wrapper HDL

- Passaggio 35: generare bitstream, esportare hardware su SDK, avviare SDK da Vivado

- Passaggio 36: SDK (senza FreeRTOS)

- Passaggio 37: Implementazione di FreeRTOS

- Passaggio 38: istruzioni per l'uso

- Passaggio 39: riferimenti e collegamenti

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:04.

- Ultima modifica 2025-01-23 14:50.

Inizia dal primo passaggio per i dettagli sulla creazione di un controller PWM servo a 2 assi.

Inizia dal diagramma a blocchi massiccio (passaggio 19) per il progetto completo.

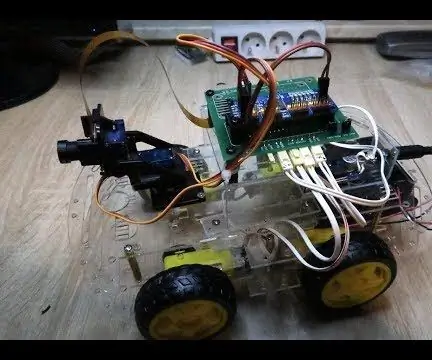

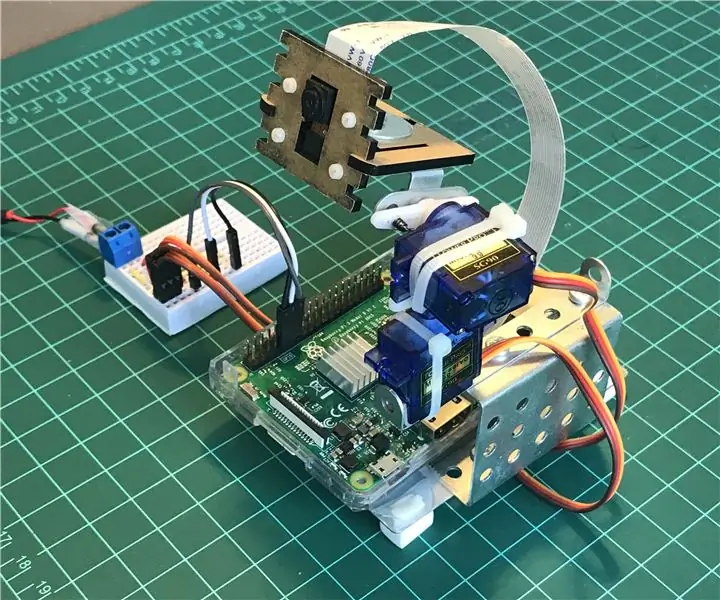

Camera + impostazione Pan/tilt che abbiamo usato:

Il PmodCON3 di Digilent è stato utilizzato per collegare i servi.

Passaggio 1: creazione di un modulo PWM - File sorgente

Passaggio 2: creazione di un modulo PWM - Configurazione Vivado

Innanzitutto, scarica la Vivado Design Suite dal sito Web Xilinx. Installa tutta la suite di design, incluso Vivado Software Development Kit (SDK). Questo progetto utilizza la versione 2017.2.

Nel frattempo, anche Digilent Adept 2 dovrebbe essere installato come driver della scheda Zybo.

Passaggio 3: creazione di un modulo PWM: creazione di un file di progetto

Prima di creare un file di progetto, assicurati di aver già installato correttamente il file Zybo come nel tutorial qui:

Vivado versione 2015.1 e successive Installazione del file di bordo

Apri Vivado 2017.2. Su Quick Start, fai clic su Crea progetto -> Avanti -> Nome progetto (Nomina il nome del tuo progetto qui) -> Tipo di progetto. In Tipo di progetto, seleziona Progetto RTL e seleziona "Non specificare fonti in questo momento". Quindi, per la parte predefinita, seleziona "Boards" e "Zybo" come nome visualizzato. Quindi, fare clic su Fine per avviare il progetto.

Passaggio 4: creazione di un modulo PWM: progettazione del blocco e impostazione del file di vincoli (I)

Su Flow Navigator, fare clic su ""Crea blocco design", quindi premere OK. fare clic sul segno "+" per aggiungere gli IP necessari. Aggiungere:

- Un sistema di elaborazione ZYNQ7 Due timer AXI

- Due AXI Timer

Passaggio 5: creazione di un modulo PWM: progettazione del blocco e impostazione del file di vincoli (II)

Dopo aver aggiunto gli IP, eseguire l'automazione dei blocchi e l'automazione della connessione. Una volta completata l'automazione, sul blocco “axi_timer_0”, fare clic destro su pwm0 -> Make External. Denominare il pin esterno pwm0 come pwm_Xaxis. Inoltre, ripeti il processo sopra sul blocco "axi_timer_1" e chiama il pin esterno pwm0 come pwm_Zaxis.

Passaggio 6: creazione di un modulo PWM: progettazione del blocco e impostazione del file di vincoli (III)

Nota che ogni volta che finiamo il Block Design in Vivado, dobbiamo creare un Wrapper HDL. Dal momento che sarà il modulo di primo livello per ogni progetto.

Passaggio 7: creazione di un modulo PWM: progettazione del blocco e impostazione del file di vincoli (IV)

Ora, dobbiamo impostare il nostro file di vincoli per assegnare i pin collegati al nostro diagramma a blocchi. Chiudi la finestra Block Design, On Sources, "Add Sources"->Aggiungi o crea vincoli-> aggiungi Zybo-Master.xdc come file di vincolo.

Passaggio 8: creazione di un modulo PWM: progettazione del blocco e impostazione del file di vincoli (V)

Aprire il file dei vincoli Zybo-Master.xdc dalla cartella Constraints, decommentare le porte che vogliamo specificare come segnali di uscita e rinominare “get_ports{XXXX}”, che XXXX denota il pin esterno denominato nel Block Diagram. L'impostazione del file dei vincoli è mostrata in figura.

Passaggio 9: creazione di un modulo PWM - Installazione hardware

Collegare i servomotori al Pmod CON3. TowerPro SG90 è il modello di servomotore che abbiamo utilizzato in questo progetto. Per i fili del servomotore, il filo arancione rappresenta il segnale PWM, collegato al pin SIG in Pmod CON3. Il filo rosso Vcc è un filo di alimentazione collegato al pin VS in Pmod CON3. Infine, il filo marrone Gnd è un filo di terra collegato al pin GND. Quindi, inserisci il Pmod CON3 nella riga superiore della porta JD nella scheda Zybo.

Passaggio 10: creazione di un modulo PWM: generazione di bitstream e avvio dell'SDK

1. Nella scheda Project Navigator, eseguire Generate BitStream.

2. Esporta hardware: File > Esporta > Esporta hardware-> seleziona “include bitstream”-> OK 3. Avvia SDK: File -> Avvia SDK.

Passaggio 11: creazione di un modulo PWM: creazione di una nuova applicazione in Xilinx SDK

Crea una nuova applicazione:

File > Nuovo > Progetto applicazione -> Inserisci il nome del tuo progetto -> Fine

In Project Explorer, dovrebbero esserci tre cartelle.

In questo caso “design_1_wrapper_hw_platform_0” è la cartella precedentemente esportata da Vivado. Axis_2_PWM_SDK_bsp è la cartella del pacchetto di supporto della scheda. E Axis_2_PWM_SDK è la nostra cartella di progetto principale in SDK. Puoi vedere il file "helloworld.c" nella cartella "src" di Axis_2_PWM_SDK, dove "helloworld.c" è il file principale.

Passaggio 12: creazione di un modulo PWM - Panoramica di Project Explorer (I)

Controlliamo alcuni file in Project Explorer. Innanzitutto, nella cartella "design_1_wrapper_hw_platform_0", apri il "system.hdf". Questo file mostra la mappa degli indirizzi per il processore ps7_cortex9 e i blocchi IP presenti nel nostro progetto.

Passaggio 13: creazione di un modulo PWM - Panoramica di Project Explorer (II)

Quindi, controlla il file "include" e "libsrc" nella cartella "Axis_2_PWM_SDK_bsp". I file di libreria qui ci consentono di interagire con le periferiche hardware senza "riprodurre" i registri.

Passaggio 14: creazione di un modulo PWM - Panoramica di Project Explorer (III)

Attraverso la documentazione BSP, xtmrctr.h si trova come una libreria Xilinx Timer Control relativa ad AXI Timer. Tipicamente, potremmo trovare qui la funzione PWM desiderata. Tuttavia, se leggi la documentazione "tmrctr_v4_3", mostra che il driver non supporta attualmente l'operazione PWM del dispositivo. A causa della carenza nella funzione PWM, dobbiamo concludere la nostra funzione PWM con l'aiuto di xtmrctr.h e AXI Timer v2.0 LogiCORE IP Product Guide.

Passaggio 15: creazione di un modulo PWM: conclusione della funzione PWM (I)

Tornando al file principale "helloworld.c", includi i seguenti file di intestazione:

Passaggio 16: creazione di un modulo PWM - Riepilogo della funzione PWM (II)

Definire gli indirizzi di base di due AXI TImer tramite “xparameters.h”.

Passaggio 17: creazione di un modulo PWM - Riepilogo della funzione PWM (III)

Crea la funzione PWM desiderata.

Duty_val: converte il valore del grado in duty cycle. PWM_Freq_Duty: imposta la frequenza e il duty cycle desiderati per generare il PWM. Dovrebbe essere assegnato anche il periodo dell'orologio.

PWM_START: assegna l'indirizzo del registro PWM e inizia a generare PWM.

PWM_STOP: assegna l'indirizzo del registro PWM e interrompe la generazione di PWM.

Il resto del codice demo è mostrato in "helloworld.c" sotto "Axis_2_PWM_SDK"

Passaggio 18: creazione di un modulo PWM: fallo funzionare

1. Programmare l'FPGA tramite SDK

- Collega Zybo Board tramite porta USB al PC.

- Xilinx Tools -> Programma FPGA

2. Esegui il programma

Fare clic sull'icona "Esegui" e selezionare il menu -> Esegui come -> Avvia su hardware

3. Terminale SDK

- Apri il terminale SDK -> Connetti a porta seriale -> OK

- Esegui il programma. Se il codice demo viene eseguito correttamente, dovresti vedere "Inizializzazione eseguita!" sul terminale SDK.

Passaggio 19: elaborazione video in streaming su Digilent ZYBO con OV7670

File di archivio completo allegato.

Passaggio 20: diagramma a blocchi completo

Questo mostra lo schema completo di tutte le connessioni e i blocchi IP nel progetto

Passaggio 21: collegare l'OV7670 a ZYBO

Creare una connessione per collegare il modulo ov7670 a ZYBO Pmods

I dati Pmod sono Pmod D

Il controllo Pmod è Pmod C

Inoltre, collega il PmodCON3 e i servi come specificato nella prima metà di questo tutorial

Passaggio 22: creare un design a blocchi

In Flow Navigator, fai clic su "Crea disegno a blocchi", quindi premi OK.

Passaggio 23: aggiungere file VHDL per il controllo e l'acquisizione della fotocamera OV7670

Aggiungi al progetto i file VHDL allegati a questo passaggio

Passaggio 24: aggiungere il file dei vincoli

Aggiungi il file dei vincoli allegato al tuo progetto.

Passaggio 25: aggiungere repository IP per IP HLS

Prendi il file Zip allegato e decomprimilo in una nuova cartella denominata in modo simile in una nuova directory (cartella) chiamata "HLS_repo".

Aggiungi un repository IP al tuo progetto andando al catalogo IP e fai clic con il pulsante destro del mouse selezionando "Aggiungi repository…"

Passa alla directory "HLS_repo" e selezionala.

Opzionale: crea tu stesso il blocco di elaborazione video HLS!

Passaggio 26: aggiungere moduli e IP

Aggiungi i moduli ov7670_axi_stream_capture, debounce e ov7670_controller allo schema a blocchi facendo clic con il pulsante destro del mouse sullo sfondo e selezionando "Aggiungi modulo…"

Allo stesso modo, aggiungi gli IP:

- HLS_Video_Track

- Scrittura buffer fotogrammi video

- Lettura buffer fotogrammi video

- Controller di temporizzazione video

- AXI4-Stream su uscita video

- 3 di "Fetta"

- Costante

- 2 di AXI Timer

Passaggio 27: impostazioni di configurazione IP

Come mostrato nelle immagini

Passaggio 28: aggiungere e configurare il blocco IP di PS

Aggiungi il sistema di elaborazione ZYNQ7 allo schema a blocchi

modifica la configurazione:

-

Configurazione PS-PL

-

HP

- Abilita S HP 0

- Abilita S HP 1

-

-

Configurazione dell'orologio

-

Orologi in tessuto PL

- FCLK_0 a 100MHz

- FCLK_1 a 25MHz (OutputClock)

- FLCK_2 a 35MHz (<=50MHz) (CameraClock)

-

Passo 29: Parte 1. Costruire un modulo PWM per servomotori

Tira fuori axi_timer_0 pwm0 nella nuova porta di uscita pwm_Xaxis

Tira fuori axi_timer_1 pwm0 nella nuova porta di uscita pwm_Zaxis

Passaggio 30: connessioni lato ingresso video (evidenziato con aclk)

Collegare correttamente i blocchi IP lato ingresso video

(* queste connessioni devono essere create selezionando le opzioni corrette durante l'automazione della connessione) "aclk" da axi_stream_capture va a:

- ap_clk sulla scrittura del buffer dei fotogrammi video

- ap_clk sul blocco di elaborazione del flusso video HLS

- *aclk su AXI smartconnect IP dal Video Frame Buffer Write a S_AXI_HP0

- *aclk corrispondente ai canali dell'AXI Interconnect IP per i canali S_AXI del blocco di elaborazione video HLS e del frame buffer video scrivere S_AXI_HP0_ACLK sul blocco PS

Il segnale del flusso video viene semplicemente collegato in serie dal blocco di acquisizione all'interfaccia di memoria Zynq.

- Il video passa dal blocco di acquisizione al blocco di elaborazione HLS.

- Il video elaborato dal blocco HLS va al blocco di scrittura del frame buffer.

- *Il blocco di scrittura frame buffer si collega all'interfaccia HP0 sul blocco Zynq PS.

- Il segnale m_axis_tuser dall'uscita del blocco di cattura è cablato manualmente sia al segnale di ingresso video_in_TUSER sul blocco di elaborazione HLS che al segnale ap_start sullo stesso blocco.

Il segnale TUSER(tuser) viene utilizzato dal protocollo di flusso video AXI per indicare l'inizio di un frame del video. AP_Start indica al blocco HLS di avviare l'elaborazione. Stiamo quindi utilizzando tuser per attivare il blocco HLS per elaborare ogni frame mentre entra. Quando si collega un singolo segnale di un bus e lo si suddivide in questo modo è necessario collegarlo anche al normale punto di terminazione del resto del bus. Vivado presuppone che se si collega il segnale manualmente si desidera disconnettere ciò a cui si collegherebbe normalmente.

Impostazioni di configurazione dei blocchi IP:

Scrittura buffer fotogrammi video:

Formati video: RGB8

1 campione per clock Max colonne: 1280 (>=640) Max righe: 960 (>=480) Max larghezza dati: 8

Passaggio 31: connessioni a OV7670

Sul blocco ov7670_axi_stream_capture

- Rendi tutti gli input esterni (fai clic con il pulsante destro del mouse su un pin e seleziona dal menu, oppure fai clic con il pulsante sinistro del mouse->ctrl+T)

- Lascia i nomi come sono

Sul blocco ov7670_controller

- Rendi tutte le uscite del blocco esterne

- Rinominare la porta config_finished in led0

- collegare clk a CameraClock (<=50MHz) (FCLK_2)

Sul blocco antirimbalzo

- collegare l'ingresso button1 a una porta di ingresso esterna chiamata btn0

- collegare l'out1 alla linea di reinvio sul blocco IP ov7670_controller

- collegare l'ingresso del pulsante2 a una porta di ingresso esterna chiamata btn3

- collegare out2n all'ingresso ext_reset_in sull'IP di ripristino del sistema del processore per il dominio del clock di acquisizione video. (*Potrebbe essere necessario farlo dopo che l'IP è stato generato*)

- collegare clk a CameraClock (<=50MHz) (FCLK_2)

Passaggio 32: connessioni sul lato uscita video

Connessioni per blocchi Video Timing Controller (VTC), AXI4-Stream to Video Out e slice

- Usa un clock a 25 MHz (FCLK_1) per vid_io_out_clk e VTC clk

- Usa 100MHz clock (FCLK_0) per aclk su AXI4-Stream to Video Out

- vtiming_out a vtiming_in

- Buffer fotogrammi video Leggi m_axis_video passa a AXI4-Stream to Video Out video_in

- vtg_ce va a gen_clken

- Collega VTC clken, aclken, vid_io_out_ce a Constant dout[0:0]

- Porta vid_hsync e vid_vsync alle porte di output esterne vga_hs e vga_vs, rispettivamente. (non nella foto)

Fette:

-

Le fette devono essere impostate come mostrato nelle immagini allegate

- rinomina i blocchi in slice_red, slice_green e slice_blue

- imposta gli intervalli di sezioni come mostrato nelle immagini per il nome del blocco

- collegare ogni uscita slice a un'uscita della porta esterna come mostrato nell'immagine.

- vid_data[23:0] si collega agli ingressi per ogni slice (Din[23:0])

Passaggio 33: eseguire blocco e automazione della connessione

Esegui Block Automation per connettere le cose dal blocco ZYNQ7 PS. Come mostrato dall'immagine.

Eseguire l'automazione della connessione per creare tutti gli IP di interconnessione. Presta molta attenzione a tutte le opzioni in ogni immagine.

Sul blocco antirimbalzo, collegare out2n all'ingresso del dominio del clock di acquisizione video Processor System Reset ext_reset_in.

Passaggio 34: Genera wrapper HDL

Genera il wrapper HDL per il tuo design a blocchi.

Impostalo come modulo superiore.

Passaggio 35: generare bitstream, esportare hardware su SDK, avviare SDK da Vivado

Assicurati di includere bitstream nell'esportazione.

La generazione del flusso di bit può richiedere molto tempo.

Quindi avvia SDK

Passaggio 36: SDK (senza FreeRTOS)

Questa versione fa tutto senza usare FreeRTOS, condensando bene il codice.

Crea un BSP autonomo basato sul design dell'hardware. Le opzioni predefinite dovrebbero andare bene. Assicurati che i sorgenti BSP siano stati generati.

Crea app come mostrato nell'immagine. (domanda vuota)

Elimina il main generato automaticamente e importa i file allegati.

Passaggio 37: Implementazione di FreeRTOS

Questa versione utilizza FreeRTOS. Crea un BSP FreeRTOS901 basato sul design dell'hardware. Le opzioni predefinite dovrebbero andare bene. Assicurati che i sorgenti BSP siano stati generati.

Crea app come mostrato nell'immagine. (domanda vuota)

Elimina il main generato automaticamente e importa i file allegati.

Passaggio 38: istruzioni per l'uso

Questo progetto è un po' difficile da avviare. Segui i passaggi in ordine.

Assicurati che il tuo ZYBO non carichi automaticamente nulla quando viene acceso. Ciò significa che il LED Done non dovrebbe accendersi. Un modo per farlo è impostare il ponticello della sorgente di avvio su JTAG.

Apri il progetto (FreeRTOS o meno) che vuoi programmare da SDK

- Accendi il tuo ZYBO. Il LED Fatto non dovrebbe accendersi.

- Programmare l'FPGA con il file bit. Il LED Fatto dovrebbe accendersi. Il led0 non deve accendersi.

- Esegui il codice (ricorda di superare il punto di interruzione iniziale se lo stai facendo).

A questo punto dovresti ricevere un output sul tuo display VGA.

Per riavviare (se si verifica un bug o altro): tocca rapidamente il pulsante PS-SRST o spegni e riaccendi ZYBO. Continua dal passaggio 2.

L'arresto del processore con il debugger farà sì che la fotocamera mantenga la posizione invece di spostarsi. Il flusso video continuerà comunque.

Passaggio 39: riferimenti e collegamenti

Guide e documentazione di riferimento Xilinx:

- PG044 - AXI-Stream su uscita video

- PG278 - Lettura/scrittura buffer frame video

Altri link:

- Il blog di Lauri - Ingresso VDMA

- Il blog di Lauri - Uscita da OV7670 a VGA utilizzando BRAM

- Wiki di Hamsterworks, di Mike Fields, la fonte originale del codice OV7670

- Scheda tecnica che mostra le specifiche di base dei tempi

Consigliato:

Meccanismo Pan e Tilt per Time Lapse DSLR: 7 passaggi (con immagini)

Meccanismo di panoramica e inclinazione per i time lapse delle reflex digitali: avevo alcuni motori passo-passo in giro e volevo davvero usarli per creare qualcosa di interessante. Ho deciso che avrei realizzato un sistema Pan and Tilt per la mia fotocamera DSLR in modo da poter creare fantastici time lapse. Articoli di cui avrai bisogno: 2x motori passo-passo -htt

Auto RasbperryPi con fotocamera FPV. Controllo tramite browser Web: 31 passaggi (con immagini)

Auto RasbperryPi con fotocamera FPV. Controllo tramite browser Web: Costruiremo un'auto 4wd - lo sterzo sarà simile a quello di un carro armato - per girare un lato delle ruote ruoterà con velocità diversa rispetto all'altro. All'auto verrà posizionata la telecamera su un supporto speciale dove potremo cambiare la posizione della telecamera. Il robot sarà c

Pan-Tilt Multi Servo Control: 11 passaggi (con immagini)

Pan-Tilt Multi Servo Control: in questo tutorial, esploreremo come controllare più servi usando Python su un Raspberry Pi. Il nostro obiettivo sarà un meccanismo PAN/TILT per posizionare una telecamera (una PiCam). Qui puoi vedere come funzionerà il nostro progetto finale:Controllo Servo Controllo loop test:

FOTOCAMERA UNICORN - Costruzione della fotocamera Raspberry Pi Zero W NoIR da 8 MP: 7 passaggi (con immagini)

UNICORN CAMERA - Fotocamera Raspberry Pi Zero W NoIR 8MP Build: Pi Zero W NoIR 8MP Camera BuildQuesto Instructable è stato creato per aiutare chiunque desideri una fotocamera a infrarossi o una fotocamera portatile davvero fantastica o una fotocamera portatile Raspberry Pi o vuole solo divertirsi, heheh . Questo è il più conveniente e configurabile

Scatta incredibili foto macro con qualsiasi fotocamera del telefono con fotocamera Soprattutto un iPhone: 6 passaggi

Scatta incredibili foto macro con qualsiasi fotocamera del telefono con fotocamera… Soprattutto un iPhone: hai mai desiderato ottenere una di quelle fantastiche foto ravvicinate… quella che dice… WOW!?… con la fotocamera di un telefono con fotocamera nientemeno !? Fondamentalmente, questo è un addon di potenziamento per qualsiasi fotocamera del telefono con fotocamera per ingrandire l'obiettivo della fotocamera esistente per prendere un w