Sommario:

- Passaggio 1: cos'è Vivado HLS?

- Passaggio 2: libreria video HLS

- Passaggio 3: Sintetizzazione

- Passaggio 4: versione e altre informazioni per l'esportazione

- Passaggio 5: esportazione in una libreria IP Vivado

- Passaggio 6: sintesi ed esportazione dell'analisi

- Passaggio 7: aggiunta della libreria IP in Vivado

- Passaggio 8: eseguire un aggiornamento

- Passaggio 9: ulteriori dettagli e informazioni

- Passaggio 10: uscita e ingresso

- Passaggio 11: interfacciamento del registro AXI

- Passaggio 12: Pragma del flusso di dati

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:04.

- Ultima modifica 2025-01-23 14:50.

Hai mai desiderato l'elaborazione in tempo reale su video senza aggiungere molta latenza o in un sistema embedded? Gli FPGA (Field Programmable Gate Arrays) sono talvolta usati per fare questo; tuttavia, scrivere algoritmi di elaborazione video in linguaggi di specifiche hardware come VHDL o Verilog è frustrante nella migliore delle ipotesi. Entra in Vivado HLS, lo strumento Xilinx che ti consente di programmare in un ambiente C++ e generare da esso il codice del linguaggio delle specifiche hardware.

Software richiesti:

- Vivado HLS

- Vivado

- (Se utilizzi i registri AXI) Vivado SDK

(Facoltativo) Scarica gli esempi realizzati da Xilinx qui:

Esempi di video Xilinx HLS

Passaggio 1: cos'è Vivado HLS?

Vivado HLS è uno strumento utilizzato per trasformare il codice simile a C++ in strutture hardware che possono essere implementate su un FPGA. Include un IDE per fare questo sviluppo. Una volta completato lo sviluppo del codice per HLS, puoi esportare il tuo IP generato in un formato per l'uso con Vivado.

Scarica i file allegati e mettili vicino a dove creerai il tuo progetto. (rinominali nuovamente in "top.cpp" e "top.h" se hanno un nome casuale)

Passaggio 2: libreria video HLS

La HLS Video Library ha la documentazione con i progetti di riferimento in questo documento: XAPP1167 Un'altra buona risorsa è la pagina Wiki di Xilinx a riguardo.

Avvia Vivado HLS.

Crea un nuovo progetto.

Prendi i file che hai scaricato nel passaggio precedente e aggiungili come file sorgente. (Nota: i file non vengono copiati nel progetto, ma rimangono invece dove sono)

Quindi utilizzare il pulsante Sfoglia per selezionare la funzione superiore.

Nella pagina successiva, seleziona la parte Xilinx che stai utilizzando.

Passaggio 3: Sintetizzazione

Soluzione => Esegui sintesi C => Soluzione attiva

Dopo ~227,218 secondi, dovrebbe essere fatto. (Nota: il tempo effettivo di sintesi varierà in base a molti fattori)

Passaggio 4: versione e altre informazioni per l'esportazione

I numeri di versione interagiscono con Vivado per consentirti di aggiornare l'IP in un progetto. Se si tratta di una modifica di versione minore, può essere eseguita mentre le modifiche principali alla versione richiedono di aggiungere manualmente il nuovo blocco e rimuovere quello vecchio. Se le interfacce non sono cambiate e l'aggiornamento della versione è minore, l'aggiornamento può essere fatto in modo completamente automatico premendo il pulsante di aggiornamento IP. Puoi eseguire "report_ip_status" nella console Vivado tcl per vedere lo stato del tuo IP.

Imposta i numeri di versione e altre informazioni in Soluzione => Impostazioni soluzione…

In alternativa, queste impostazioni possono essere impostate durante l'esportazione.

Passaggio 5: esportazione in una libreria IP Vivado

Soluzione => Esporta RTL

Se non hai impostato i dettagli della libreria IP nel passaggio precedente, puoi farlo ora.

Passaggio 6: sintesi ed esportazione dell'analisi

In questa schermata possiamo vedere le statistiche sul nostro modulo esportato, mostrando che soddisfa il nostro periodo di clock di 10 ns (100 MHz) e quanta risorsa utilizza.

Con una combinazione di questo, il nostro rapporto di sintesi e la nostra analisi del flusso di dati, possiamo vedere che ci vogliono 317338 cicli di clock * periodo di clock di 10 ns * 14 fasi della pipeline = 0,04442732 secondi. Ciò significa che la latenza totale aggiunta dalla nostra elaborazione delle immagini è inferiore a un ventesimo di secondo (quando con clock a 100 MHz mirati).

Passaggio 7: aggiunta della libreria IP in Vivado

Per utilizzare il tuo blocco IP sintetizzato dovrai aggiungerlo a Vivado.

In Vivado aggiungi un repository IP al tuo progetto andando al catalogo IP e fai clic con il tasto destro del mouse selezionando "Aggiungi repository…"

Passare alla directory del progetto Vivado HLS e selezionare la directory della soluzione.

Dovrebbe riportare l'IP che ha trovato.

Passaggio 8: eseguire un aggiornamento

A volte è necessario apportare modifiche al blocco HLS dopo averlo incluso in un progetto Vivado.

Per fare ciò, puoi apportare le modifiche e risintetizzare ed esportare l'IP con un numero di versione più alto (vedi i dettagli nel passaggio precedente sulle modifiche al numero di versione principale/minore).

Dopo aver modificato l'esportazione della nuova versione, aggiorna i tuoi repository IP in Vivado. Questo può essere fatto quando Vivado nota che l'IP è cambiato nel repository, o attivato manualmente. (Nota, se aggiorni i tuoi repository IP dopo l'avvio, ma prima che l'esportazione sia completata in HLS, l'IP non sarà temporaneamente presente, attendi che finisca e si aggiorni di nuovo.)

A questo punto dovrebbe apparire una finestra con le informazioni che un IP è stato modificato sul disco e ti dà la possibilità di aggiornarlo con un pulsante "Aggiorna selezionato". Se la modifica è stata una modifica di versione minore e nessuna delle interfacce è cambiata, quindi premendo quel pulsante si sostituirà automaticamente il vecchio IP con quello nuovo, altrimenti potrebbe essere necessario più lavoro.

Passaggio 9: ulteriori dettagli e informazioni

I seguenti passaggi forniscono ulteriori informazioni su come funziona la sintesi HLS e cosa puoi fare con essa.

Per un esempio di un progetto che utilizza un blocco IP sintetizzato HLS, vedere questo istruibile.

Passaggio 10: uscita e ingresso

Gli output e gli input al blocco IP finale sono determinati da un'analisi che il sintetizzatore fa del flusso di dati in entrata e in uscita dalla funzione superiore.

Simile a VHDL o verilog, HLS consente di specificare i dettagli sulle connessioni tra IP. Queste righe ne sono un esempio:

void image_filter(AXI_STREAM& video_in, AXI_STREAM& video_out, int& x, int& y) {

#pragma HLS INTERFACE axis port=video_in bundle=INPUT_STREAM #pragma HLS INTERFACE axis port=video_out bundle=OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port=x bundle=CONTROL_BUS offset=0x14#pragma HLS INTERFACE s_axilite port=y bundle=CONTROL_BUS offset=0x

Puoi vedere come le porte mostrate sul blocco IP sono influenzate da queste direttive.

Passaggio 11: interfacciamento del registro AXI

Per ottenere input/output da/verso il blocco IP al PS, un buon modo per farlo è tramite un'interfaccia AXI.

Puoi specificarlo nel tuo codice HLS, inclusi gli offset da utilizzare per accedere al valore in un secondo momento in questo modo:

void image_filter(AXI_STREAM& video_in, AXI_STREAM& video_out, int& x, int& y) {

#pragma INTERFACCIA HLS s_axilite port=x bundle=CONTROL_BUS offset=0x14

#pragma HLS INTERFACE s_axilite port=y bundle=CONTROL_BUS offset=0x1C #pragma HLS dataflow

x = 42;

y = 0xDEADBEEF; }

Una volta connesso correttamente in Vivado, puoi accedere ai valori utilizzando questo codice in Vivado SDK:

#include "parametri.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32(XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32(XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Questo ti farà finire con 42 in x e 0xdeadbeef in y

Passaggio 12: Pragma del flusso di dati

All'interno del #pragma DATAFLOW il modo in cui il codice è implementato cambia dal normale C++. Il codice è in pipeline in modo che tutte le istruzioni siano sempre in esecuzione in diverse parti dei dati (si pensi a una catena di montaggio in una fabbrica, ogni stazione lavora continuamente eseguendo una funzione e passandola alla stazione successiva)

dall'immagine si vede che ognuna delle direttive

Nonostante sembrino normali variabili, gli oggetti img sono in realtà implementati come piccoli buffer tra i comandi. L'utilizzo di un'immagine come input di una funzione la "consuma" e la rende non più utilizzabile. (Da qui la necessità dei comandi duplicati)

Consigliato:

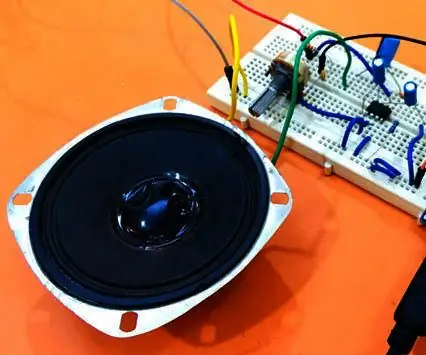

Motore passo-passo controllato via MIDI con un chip di sintesi digitale diretta (DDS): 3 passaggi

Motore passo-passo controllato via MIDI con un chip DDS (Direct Digital Synthesis): hai mai avuto una cattiva idea di doverti SOLO trasformare in un mini progetto? Beh, stavo scherzando con uno schizzo che avevo realizzato per Arduino Due finalizzato a fare musica con un modulo AD9833 Direct Digital Synthesis (DDS)… e ad un certo punto ho pensato &q

Sintesi vocale Fare clic su un UChip alimentato da ARMbasic e altri SBC alimentati da ARMbasic: 3 passaggi

Sintesi vocale Fare clic su un UChip alimentato da ARMbasic e altri SBC alimentati da ARMbasic: Introduzione: buona giornata. Mi chiamo Tod. Sono un professionista aerospaziale e della difesa che è anche un po' geek nel cuore. Ispirazione: provengo dall'era delle BBS dial-up, microcontrollori a 8 bit, personal computer Kaypro/Commodore/Tandy/TI-994A, quando R

Convertitore di sintesi vocale Arduino utilizzando LM386 - Progetto Arduino Parlante - Libreria Talkie Arduino: 5 passaggi

Convertitore di sintesi vocale Arduino utilizzando LM386 | Progetto Arduino Parlante | Talkie Arduino Library: Ciao ragazzi, in molti progetti richiediamo ad arduino di parlare qualcosa come l'orologio parlante o di dire alcuni dati, quindi in queste istruzioni convertiremo il testo in parlato usando Arduino

Sintesi vocale retrò. Parte: 12 IoT, Domotica: 12 passaggi (con immagini)

Sintesi vocale retrò. Parte: 12 IoT, automazione domestica: questo articolo è il dodicesimo di una serie sugli Instructables sull'automazione domestica che documentano come creare e integrare un dispositivo di sintesi vocale retrò IoT in un sistema di automazione domestica esistente, incluse tutte le funzionalità software necessarie per abilitare t

Riconoscimento vocale svincolato e sintesi in spagnolo per Arduino: 11 passaggi

Reconocimiento De Voz Desconectado Y Síntesis En Español Para Arduino: This Instructable è disponibile anche in inglese.MOVI significa 'My Own Voice Interface' (Mi propia interfaz de voz) y es un escudo para el Arduino. Con MOVI costruire sui propri loghi di voce per controllare i dispositivi all'interno dell'IDE di Ar