Sommario:

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:03.

- Ultima modifica 2025-06-01 06:09.

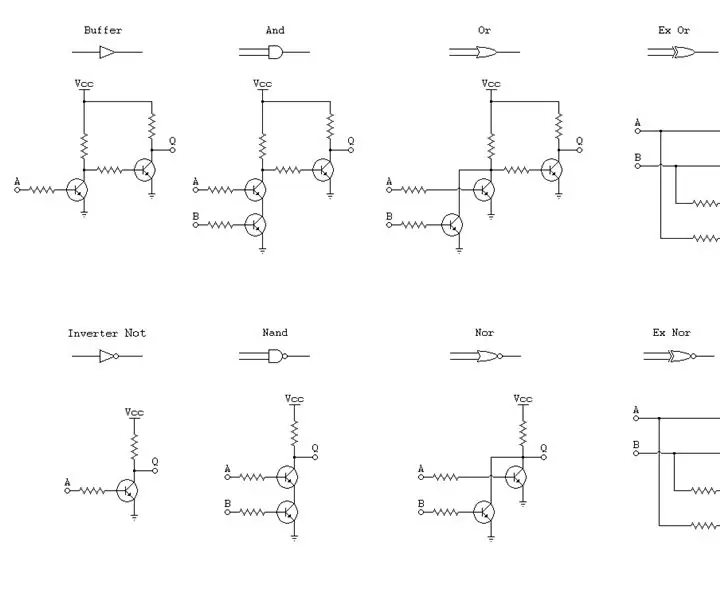

Costruisco gate a transistor un po' diversi dalla maggior parte degli altri ingegneri elettronici. La maggior parte delle persone quando costruiscono gate a transistor; costruiscili con in mente solo la logica positiva, tuttavia le porte nei circuiti integrati hanno due logiche, logica positiva e logica negativa. E costruisco i miei gate a transistor con logica positiva e negativa.

Sebbene ci siano otto porte; Buffer, Inverter or Not, And, Nand, Or, Nor, Xor e Xnor, sono costituiti da tre circuiti di gate. E quando si costruiscono porte logiche doppie, i tre circuiti utilizzati per costruire una porta sono Inverter o No, Nand e Nor, il resto delle porte è costituito da due o più di queste tre porte.

Perché costruire gate a transistor? Bene, ecco cinque motivi per costruire i tuoi cancelli.

1. Non hai il cancello di cui hai bisogno.

2. Vuoi un gate che trasporta più potenza di un gate IC standard.

3. Vuoi solo un cancello e odi sprecare il resto dei cancelli sull'IC.

4. Costo, un inverter a un transistor è inferiore a $ 0,25 e un IC inverter esadecimale è $ 1,00 e oltre.

5. Vuoi capire meglio i cancelli.

Passaggio 1: strumenti e parti

Le porte in questo Instructable sono porte da ¼ watt se vuoi costruire porte con una potenza maggiore avrai bisogno di componenti con una potenza maggiore.

Cavi per ponticelli

tagliere

Alimentazione elettrica

1 x SN74LS04 IC

2 x interruttori

2 x LED 1 rosso 1 verde

2 x 820 ¼ w resistori

2 x 1 kΩ ¼ w resistori

3 x 10 kΩ ¼ w resistori

3 x NPN transistor per uso generale, ho usato 2N3904.

2 x transistor PNP per uso generale, ho usato 2N3906.

Passaggio 2: doppia logica

Quando guardi la tavola della verità di un cancello; come una porta Or a due ingressi, otterrai una tabella di verità simile a questa. Questa è una tabella di verità positiva per una porta Or. Sotto A e B sono gli ingressi al cancello e Q è l'uscita. 1 rappresenta un valore logico di 1 o + 5 volt e 0 rappresenta un valore logico di 0 o 0 volt. Quindi, quando la maggior parte delle persone costruisce un gate con i transistor, lo costruisce con un valore logico di 1 o + 5 volt e un valore logico di 0 o nessun volt. Ma non è quello che succede all'uscita di un gate, in un IC.

Quando l'uscita di una porta va dal valore logico 1 al valore logico 0, l'uscita di quella porta va da + 5 volt con la corrente che fluisce dall'uscita a 0 volt con la corrente che fluisce nell'uscita della porta. La corrente inverte la direzione. Quando si utilizza il flusso di corrente inversa, questo è chiamato logica negativa dove 0 volt è - 1 valore logico e + 5 volt è - 0 valore logico.

È più facile vedere cosa fa quando si collega l'uscita di qualsiasi gate; alla base di un transistor NPN e di un transistor PNP, in serie con un LED. Mentre l'uscita del gate è a valore logico 1, (5 Volt), il transistor NPN è chiuso e il led in serie al transistor NPN si accende. Quando l'uscita del gate passa dal valore logico 1 al valore logico 0 (da 5 volt a 0 volt), la corrente inverte la direzione e il transistor NPN si apre alla chiusura del transistor PNP. Questo spegne il LED in serie al transistor NPN e accende il LED in serie al transistor PNP.

Le mie porte a transistor hanno la stessa doppia logica delle porte nei circuiti integrati. Mentre l'uscita del gate è a valore logico 1, (5 Volt), il transistor NPN è chiuso e il led in serie al transistor NPN si accende. Quando l'uscita del gate passa dal valore logico 1 al valore logico 0 (da 5 volt a 0 volt), la corrente inverte la direzione e il transistor NPN si apre alla chiusura del transistor PNP. Questo spegne il LED in serie al transistor NPN e accende il LED in serie al transistor PNP.

Passaggio 3: non o cancello inverter

La porta Not o Inverter è la prima delle 3 porte necessarie per realizzare le altre 5 porte.

Quando l'ingresso, (A) del gate dell'inverter è 0 o 0 volt, il transistor NPN è aperto e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Quando l'ingresso, (A) del gate dell'inverter è 1 o +5 volt, il transistor NPN è chiuso e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso il transistor.

Passaggio 4: Nand Gate

Il cancello Nand è il secondo dei tre cancelli necessari per realizzare gli altri 5 cancelli.

Quando gli ingressi, (A e B) della porta Nand sono 0 o 0 volt, entrambi i transistor NPN sono aperti e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Quando l'ingresso, (A) della porta Nand è 1 o +5 volt, il transistor NPN sull'ingresso A è chiuso. E quando l'ingresso, (B) della porta Nand è 0 o 0 volt, il transistor NPN sull'ingresso B è aperto e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Quando l'ingresso, (A) della porta Nand è 0 o 0 volt, il transistor NPN sull'ingresso A è aperto. E quando l'ingresso, (B) della porta Nand è 1 o +5 volt, il transistor NPN sull'ingresso B è chiuso e l'uscita, (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Quando gli ingressi (A e B) della porta Nand sono 1 o +5 volt, entrambi i transistor NPN sono chiusi e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso i transistor.

Passaggio 5: né cancello

La porta Nor è la terza delle tre porte necessarie per realizzare le altre 5 porte.

Quando gli ingressi (A e B) della porta Nor sono 0 o 0 volt entrambi i transistor NPN sono aperti e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Quando l'ingresso, (A) della porta Nor è 1 o +5 volt, il transistor NPN sull'ingresso A è chiuso. E quando l'ingresso, (B) della porta Nor è 0 o 0 volt, il transistor NPN sull'ingresso B è aperto e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso il transistor sull'ingresso A.

Quando l'ingresso, (A) della porta Nor è 0 o 0 volt, il transistor NPN sull'ingresso A è aperto. E quando l'ingresso, (B) della porta Nor è 1 o +5 volt, il transistor NPN sull'ingresso B è chiuso e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso il transistor su B ingresso.

Quando gli ingressi (A e B) della porta Nor sono 1 o +5 volt, entrambi i transistor NPN sono chiusi e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso entrambi i transistor.

Passaggio 6: tampone

Un Buffer usa due delle stesse porte; due porte Not o Inverter in serie.

Quando l'ingresso, (A) del primo gate dell'invertitore è 0 o 0 volt, il transistor NPN è aperto e l'uscita è 1 o +5 volt all'ingresso del secondo inverter. Quando l'ingresso del secondo gate dell'invertitore è 1 o +5 volt, il transistor NPN è chiuso e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso il transistor.

Quando l'ingresso, (A) del primo gate dell'invertitore è 1 o +5 volt, il transistor NPN è chiuso e l'uscita è 0 o 0 volt all'ingresso del secondo inverter. Quando l'ingresso del secondo gate dell'inverter è 0 o 0 volt, il transistor NPN è aperto e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Passaggio 7: e il cancello

La porta And è una porta Nand e una porta Not o Inverter in serie.

Gli ingressi sono gli stessi del gate Nand, tuttavia l'uscita è invertita dal gate Not o Inverter.

Quando gli ingressi (A e B) della porta And sono 0 o 0 volt entrambi i transistor NPN sono aperti, l'uscita della prima porta è 1 o +5 volt. Quando l'ingresso del gate dell'inverter è 1 o +5 volt, il transistor NPN è chiuso e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso il transistor.

Quando l'ingresso, (A) della porta And è 1 o +5 volt, il transistor NPN sull'ingresso A è chiuso. E quando l'ingresso, (B) della porta And è 0 o 0 volt, il transistor NPN sull'ingresso B è aperto, l'uscita della prima porta è 1 o +5 volt. Quando l'ingresso del gate dell'inverter è 1 o +5 volt, il transistor NPN è chiuso e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso il transistor.

Quando l'ingresso, (A) della porta And è 0 o 0 volt, il transistor NPN sull'ingresso A è aperto. E quando l'ingresso, (B) della porta And è 1 o +5 volt, il transistor NPN sull'ingresso B è chiuso, l'uscita della prima porta è 1 o +5 volt. Quando l'ingresso del gate dell'inverter è 1 o +5 volt, il transistor NPN è chiuso e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso il transistor.

Quando gli ingressi (A e B) della porta Nand sono 1 o +5 volt, entrambi i transistor NPN sono chiusi e l'uscita della prima porta è 0 o 0 volt. Quando l'ingresso del gate dell'inverter è 0 o 0 volt, il transistor NPN è aperto e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Passaggio 8: o cancello

La porta Or è una porta Nor e una porta Not o Inverter in serie.

Gli ingressi sono gli stessi del gate Nor, tuttavia l'uscita è invertita dal gate Not o Inverter.

Quando gli ingressi (A e B) della porta Or sono 0 o 0 volt entrambi i transistor NPN sono aperti, l'uscita della prima porta è 1 o +5 volt. Quando l'ingresso del gate dell'inverter è 1 o +5 volt, il transistor NPN è chiuso e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso il transistor.

Quando l'ingresso, (A) della porta Or è 1 o +5 volt, il transistor NPN sull'ingresso A è chiuso. E quando l'ingresso, (B) della porta Nor è 0 o 0 volt, il transistor NPN sull'ingresso B è aperto e l'uscita della prima porta è 0 o 0 volt. Quando l'ingresso del gate dell'inverter è 0 o 0 volt, il transistor NPN è aperto e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Quando l'ingresso, (A) della porta Or è 0 o 0 volt, il transistor NPN sull'ingresso A è aperto. E quando l'ingresso, (B) della porta Nor è 1 o +5 volt, il transistor NPN sull'ingresso B è chiuso e l'uscita della prima porta è 0 o 0 volt. Quando l'ingresso del gate dell'inverter è 0 o 0 volt, il transistor NPN è aperto e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Quando gli ingressi (A e B) della porta Or sono 1 o +5 volt, entrambi i transistor NPN sono chiusi e l'uscita della prima porta è 0 o 0 volt. Quando l'ingresso del gate dell'inverter è 0 o 0 volt, il transistor NPN è aperto e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Passaggio 9: Esclusivo Nor Gate (Xnor)

La porta Nor Exclusive è configurata come due porte Nand collegate in parallelo come una porta Nor con i due transistor PNP dei transistor superiori.

Quando gli ingressi (A e B) della porta Xnor sono 0 o 0 volt entrambi i transistor NPN sono aperti ed entrambi i transistor PNP sono chiusi. L'uscita, (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Quando l'ingresso, (A) della porta Xnor è 1 o +5 volt, il transistor NPN sull'ingresso A è chiuso e il transistor PNP è aperto. Con l'ingresso, (B) della porta Xnor è 0 o 0 volt il transistor PNP sull'ingresso B è chiuso e il transistor NPN è aperto. L'uscita, (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso i transistor chiusi.

Quando l'ingresso, (A) della porta Xnor è 0 o 0 volt, il transistor NPN sull'ingresso A è aperto e il transistor PNP è chiuso. Con l'ingresso (B) della porta Xnor è 1 o +5 volt il transistor PNP sull'ingresso B è aperto e il transistor NPN è chiuso. L'uscita, (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso i transistor chiusi.

Quando gli ingressi (A e B) della porta Xnor sono 1 o +5 volt entrambi i transistor NPN sono chiusi ed entrambi i transistor PNP sono aperti. L'uscita, (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Passaggio 10: Esclusivo o Gate (Xor)

Il cancello esclusivo Or; utilizza tutte e tre le porte chiave, è configurato come due porte Nand collegate in parallelo come una porta Nor con i due transistor PNP dei transistor superiori e una porta Not o Inverter in serie.

Gli ingressi del gate Xor sono gli stessi del gate Xnor, tuttavia l'uscita è invertita dal gate Not o Inverter.

Quando gli ingressi (A e B) della porta Xnor sono 0 o 0 volt entrambi i transistor NPN sono aperti ed entrambi i transistor PNP sono chiusi e l'uscita della prima serie di porte è 1 o +5 volt. Quando l'ingresso del gate dell'inverter è 1 o +5 volt, il transistor NPN è chiuso e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso il transistor.

Quando l'ingresso, (A) della porta Xnor è 1 o +5 volt, il transistor NPN sull'ingresso A è chiuso e il transistor PNP è aperto. Con l'ingresso (B) della porta Xnor è 0 o 0 volt il transistor PNP sull'ingresso B è chiuso e il transistor NPN è aperto, 0 o 0 volt all'ingresso dell'inverter. Quando l'ingresso del gate dell'inverter è 0 o 0 volt, il transistor NPN è aperto e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Quando l'ingresso, (A) della porta Xnor è 0 o 0 volt, il transistor NPN sull'ingresso A è aperto e il transistor PNP è chiuso. Con l'ingresso (B) della porta Xnor è 1 o +5 volt il transistor PNP sull'ingresso B è aperto e il transistor NPN è chiuso, 0 o 0 volt all'ingresso dell'inverter. Quando l'ingresso del gate dell'inverter è 0 o 0 volt, il transistor NPN è aperto e l'uscita (Q) è 1 o +5 volt e qualsiasi corrente positiva esce dall'uscita (Q).

Quando gli ingressi, (A e B) del gate Xnor è 1 o +5 volt entrambi i transistor NPN sono chiusi ed entrambi i transistor PNP sono aperti Quando l'ingresso del secondo gate Inverter è 1 o +5 volt NPN il transistor è chiuso e l'uscita (Q) è 0 o 0 volt e qualsiasi corrente positiva va a massa attraverso il transistor.

Secondo classificato nella sfida Consigli e trucchi per l'elettronica

Consigliato:

Come realizzare un'antenna doppia biQuade 4G LTE Semplici passaggi: 3 passaggi

Come realizzare un'antenna doppia biQuade 4G LTE Semplici passaggi: La maggior parte delle volte che ho affrontato, non ho una buona potenza del segnale per i miei lavori quotidiani. Così. Cerco e provo diversi tipi di antenna ma non funziona. Dopo aver perso tempo ho trovato un'antenna che spero di realizzare e testare, perché è principio costruttivo non

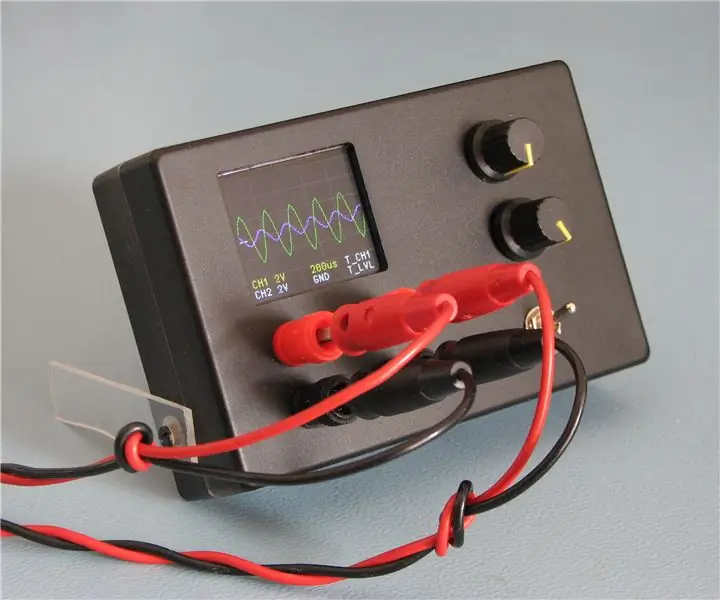

Oscilloscopio a doppia traccia: 11 passaggi (con immagini)

Oscilloscopio a doppia traccia: quando ho costruito il mio precedente mini oscilloscopio volevo vedere quanto bene potevo far funzionare il mio microcontrollore ARM più piccolo, un STM32F030 (F030), e ha fatto un buon lavoro. In uno dei commenti è stato suggerito che una "Pillola Blu" con un STM32F103

Antenna radioamatoriale VHF/UHF a doppia banda a quarto d'onda di Asni Nor Rizwan: 10 passaggi

Antenna radioamatoriale VHF/UHF a doppia banda a quarto d'onda di Asni Nor Rizwan: un semplice & L'antenna dual band economica ti farà risparmiare due antenne diverse per UHF e VHF

Server dati IoT a doppia temperatura: 12 passaggi (con immagini)

Server dati IoT a doppia temperatura: questo è il mio primo tentativo di scrivere un Instructable e quindi per favore vacci piano con me! Se pensi che questo non sia male, per favore votami per il First Time Author Contest. Questo è il mio progetto Lock-Down per monitorare a distanza 2 temperature in una serra

Luci automatiche collegate al monitoraggio di porte e porte.: 5 passaggi

Luci automatiche collegate al monitoraggio delle porte e delle porte.: Sembra essere molto difficile trovare il quadro elettrico al buio, ma questo progetto è davvero utile per risolvere questo problema. Segui i passaggi seguenti per conoscere la soluzione di questo