Sommario:

- Passaggio 1: configurare la logica programmabile Zynq per il trasmettitore

- Passaggio 2: configurare la logica programmabile Zynq per il ricevitore

- Passaggio 3: configurazione del driver VDMA

- Passaggio 4: configurazione della rete nanorouter

- Passaggio 5: configurazione del sistema di elaborazione Zynq per la trasmissione dei dati tramite Ethernet

- Passaggio 6: configurazione del sistema di elaborazione Zynq per la ricezione dei dati tramite Ethernet

- Passaggio 7: collega le tue schede Zybo alla sorgente HDMI e al dissipatore HDMI

- Passaggio 8: idee alternative per il miglioramento

- Passaggio 9: accessibilità

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:03.

- Ultima modifica 2025-01-23 14:49.

Hai mai desiderato di poter collegare la tua TV a un PC o laptop come monitor esterno, ma non volevi avere tutti quei fastidiosi cavi di intralcio? Se è così, questo tutorial è solo per te! Mentre ci sono alcuni prodotti che raggiungono questo obiettivo, un progetto fai-da-te è molto più soddisfacente e potenzialmente più economico.

Questo concetto è diverso da prodotti come Chromecast, poiché è destinato a sostituire un cavo HDMI che si collega a un monitor invece di essere un dispositivo di streaming.

Il nostro progetto è stato creato come progetto finale per un corso di sistemi operativi in tempo reale presso la California State Polytechnic University, San Luis Obispo.

L'obiettivo del progetto è utilizzare due schede Digilent Zybo per fungere da interfaccia di comunicazione wireless tra un dispositivo trasmettitore HDMI (PC, blu-ray, ecc.) e un dispositivo ricevente HDMI (monitor desktop, proiettore, TV, ecc.).

Un Digilent Zybo sarà collegato tramite HDMI al dispositivo di trasmissione e l'altro sarà collegato tramite HDMI al dispositivo di ricezione.

La comunicazione wireless verrà effettuata utilizzando una rete locale wireless dedicata al trasmettitore e al ricevitore, senza essere instradata attraverso un router domestico o altro dispositivo simile. Il modulo wireless utilizzato per questo progetto è il nanorouter tplink wr802n, uno dei quali funziona come punto di accesso per stabilire la rete e l'altro come client per connettersi alla rete. Ogni nanorouter sarà collegato tramite cavo ethernet a una delle schede Zybo. Quando sono connessi a questi router, i dispositivi comunicheranno tramite TCP come se fossero collegati con un unico cavo ethernet (il che significa che l'unica configurazione necessaria per stabilire una connessione è l'indirizzo IP del client).

Sebbene l'obiettivo del progetto fosse quello di facilitare un flusso di video 1080x720 a 60Hz, ciò non è stato possibile a causa delle limitazioni di larghezza di banda nella rete wireless e della mancanza di compressione video in tempo reale per ridurre i dati necessari per l'invio. Invece, questo progetto funge da struttura per lo sviluppo futuro per raggiungere questo obiettivo, poiché ha limitazioni severamente limitate nella frequenza dei fotogrammi per trasmettere correttamente i dati HDMI come previsto.

Requisiti del progetto:

2x schede di sviluppo Digilent Zybo (deve avere almeno una porta HDMI)

2x cavi HDMI

2x cavi microusb (per collegare Zybo al PC per lo sviluppo)

2x nanorouter tplink wr802n (inclusi adtl. 2x microusb e adattatori di alimentazione per presa a muro)

2x cavi ethernet

***Nota: questo tutorial presuppone la familiarità con la suite di design Vivado e l'esperienza nella creazione di un nuovo progetto e del design a blocchi.***

Passaggio 1: configurare la logica programmabile Zynq per il trasmettitore

Il nostro approccio allo sviluppo della logica programmabile del trasmettitore è stato quello di eseguire un pass-through hdmi-hdmi dal PC al monitor utilizzando due blocchi Video Direct Memory Access (VDMA), uno per la scrittura e uno per la lettura.

Entrambi sono selezionati per la modalità a 3 frame buffer (0-1-2) a esecuzione libera. Poiché il core video è ottimizzato per 60 frame al secondo, ciò significa che il VDMA scriverà o leggerà un nuovo frame ogni 16,67 ms in questo ordine: 0, 1, 2, 0, 1, 2, 0, 1, 2. Le posizioni di memoria DDR per ogni frame sono diverse per i due VDMA perché non sono più sincronizzate tra loro. Viene invece utilizzato un timer hardware (TTC1), configurato per 60 Hz, per sincronizzare il movimento dei dati tra le due locazioni di memoria.

L'immagine sopra mostra 3 frame, le loro dimensioni e la quantità di memoria richiesta da ciascuno (a destra del frame). Se assegniamo la scrittura VDMA a queste locazioni di memoria, allora possiamo assegnare le locazioni di memoria VDMA lette oltre questo set, diciamo a partire da 0x0B000000. Ogni frame è composto da 1280*720 pixel e ogni pixel è composto da 8 bit di Rosso, Verde e Blu per un totale di 24 bit. Ciò significa che un frame è composto da 1280*720*3 byte (2,76 MB).

All'interno del timer IRQ, che è descritto nella configurazione del driver VDMA, gestirà la copia dei dati tra le due locazioni di memoria VMDA. Il VDMA fornisce un puntatore al frame corrente in cui viene scritto o letto. Il frame è rappresentato da un particolare codice gray, che viene convertito in software. Le definizioni del codice grigio per una configurazione a 3 frame-buffer sono disponibili nella Guida del prodotto AXI VDMA nell'appendice C.

Questo ci permette di copiare i contenuti scritti in memoria senza leggere da un frame attualmente in scrittura.

***Notare che il VDMA letto non viene utilizzato quando si inviano dati attraverso la rete wireless. Il suo unico scopo è verificare il corretto funzionamento della copia della memoria dal VMDA di scrittura. La lettura VMDA dovrebbe essere disabilitata.***

Ecco i passaggi per creare il Transmitter Design Block:

- Quando si crea un nuovo progetto, è una buona idea assegnare un chip o una scheda al progetto. Questo collegamento descrive come aggiungere nuovi file di bacheca alla directory Vivado e associare la bacheca corretta al tuo progetto. Sarà utile quando si aggiunge il blocco Processing System e si passa dall'hardware al software (lato SDK).

-

Aggiungi i seguenti blocchi:

- dvi2rgb

- Video in Axi4-stream

- Controllore di temporizzazione

- axi4-stream per video out

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Procedura guidata dell'orologio

- Costante

- Sistema di elaborazione Zynq

- Quando si aggiunge il sistema di elaborazione, fare clic su "Esegui automazione blocco" dalla barra colorata in alto in verde e assicurarsi che l'opzione "Applica preimpostazione scheda" sia selezionata. Lascia tutto il resto predefinito.

- Le immagini di ogni finestra di configurazione del blocco possono essere trovate nelle immagini sopra. Se non vedi un'immagine per una particolare finestra, lasciala come predefinita.

-

Inizia a configurare il sistema di elaborazione Zynq:

- Nella configurazione PS-PL AXI Non Secure Enable GP Master AXI, abilita l'interfaccia M AXI GP0

- Nella configurazione PS-PL HP Slave AXI Interface, abilitare sia HP0 che HP1

- In MIO Configuration Assicurarsi che ENET0 sia abilitato in I/O Peripherals, quindi Application Processor Unit, abilitare Timer0

- In Clock Configuration PL Fabric Clocks, abilitare FCLK_CLK0 e impostare su 100 MHz.

- Fare clic su OK

- Prima di fare clic su "Esegui automazione connessione", assicurati di collegare i blocchi video come mostrato nell'immagine di progettazione del blocco TX sopra. Dovrai rinominare la costante in VDD e impostare il valore su 1. Collega i blocchi video di conseguenza.

- Rendi l'orologio HDMI TMDS e i pin dati esterni sui blocchi rgb2dvi e dvi2rgb

- Creare una porta di input e output per il segnale di rilevamento hot plug (HPD) e collegarli insieme, questi sono definiti nel file dei vincoli

-

Il pixel clock viene recuperato da TMDS_Clk_p, che viene creato nel file dei vincoli. Questo sarà 74,25 MHz in conformità con la risoluzione 720p. È importante collegare il pixel clock (dal blocco dvi2rgb) ai seguenti pin:

- vid_io_in_clk (video in blocco flusso assi)

- vid_io_out_clk (stream axi per vid out block)

- clk (controllore di temporizzazione)

- PixelClk (rgb2dvi)

- ***Nota: attualmente, per attivare il ripristino del pixel clock, i connettori HDMI rx e tx devono essere collegati a una sorgente/sink attivo. Un modo per aggirare questo problema è separare i blocchi video rx e tx in diversi domini di clock (in altre parole, generare un nuovo clock a 74,25 MHz da inviare al blocco tx).***

- Quindi imposta la procedura guidata dell'orologio in modo da avere un input di 100 MHz (sorgente buffer globale) e 3 clock di output a 50 MHz (clock AXI-Lite), 150 MHz (clock AXI4-Stream), 200 MHz (pin dvi2rgb RefClk).

- Collegare il pin del sistema di elaborazione FCLK_CLK0 all'ingresso della procedura guidata dell'orologio

- A questo punto clicca "Esegui automazione connessione" dalla barra verde nella parte superiore della finestra di progettazione. È una buona idea farlo per un blocco alla volta e seguire l'immagine di progettazione del blocco TX sopra.

- Lo strumento tenterà di aggiungere l'AXI Interconnect, che funge da interconnessione master/slave per i blocchi che utilizzano il bus AXI-Lite (VDMA e GPIO).

- Aggiungerà anche AXI SmartConnect, che funge da interconnessione master/slave per le interfacce del processore AXI4-Stream e High Performance utilizzate dal VDMA (Stream to Memory Map e viceversa).

- Lo strumento aggiungerà anche un ripristino del sistema del processore. Assicurati che questo sia collegato solo ai VDMA, GPIO e blocchi relativi al processore. Non collegarlo a nessun blocco video (es. dvi2rgb, controller di temporizzazione, vid to stream ecc.)

- Una volta completata l'automazione della connessione, verificare che le connessioni corrispondano a quelle dell'immagine di progettazione del blocco TX. Noterai un blocco ILA di sistema aggiuntivo che non è stato menzionato. Questo è solo per il debug e non è necessario per ora. Utilizza il ripristino del processore da 150 M, quindi non è nemmeno necessario. Ovunque vedi piccoli "bug" verdi sugli autobus, è a causa dell'ILA e può essere ignorato.

- Il passaggio finale consiste nel fare clic con il pulsante destro del mouse sul design del blocco nell'albero dei sorgenti del progetto e selezionare "Crea HDL Wrapper". Se prevedi di aggiungere logica al wrapper, verrà sovrascritto ogni volta che viene selezionato.

- Vedere la sezione Configurazione del driver VDMA per i dettagli sul lato SDK.

Orologi e azzeramenti

Ho scoperto che gli aspetti più importanti di qualsiasi progetto di logica programmabile è un'attenta considerazione dei domini di clock e dei segnali di ripristino. Se sono configurati correttamente, hai buone possibilità di far funzionare il tuo progetto.

Pixel Clock e temporizzazione bloccati

Per verificare che alcuni segnali siano attivi, è buona norma legare questi segnali ai LED (orologi, reset, blocchi ecc.). Due segnali che ho trovato utile da tracciare sulla scheda del trasmettitore sono stati il pixel clock e il segnale "bloccato" sul blocco AXI4-Stream to video out, che ti dice che la temporizzazione video è stata sincronizzata con il controller di temporizzazione e la sorgente video dati. Ho aggiunto una logica al wrapper del blocco di progettazione che tiene traccia del pixel clock utilizzando il segnale PixelClkLocked sul blocco dvi2rgb come ripristino. Ho allegato il file come hdmi_wrapper.v qui. Il file dei vincoli è anche allegato qui.

Passaggio 2: configurare la logica programmabile Zynq per il ricevitore

Il blocco logico programmabile per il ricevitore è più semplice. La differenza chiave, oltre ai blocchi di input hdmi mancanti, è l'assenza di un pixel clock recuperato. Per questo motivo dobbiamo generare il nostro dalla procedura guidata dell'orologio. Questo progetto dovrebbe essere eseguito in un progetto separato dal trasmettitore. Per i nostri scopi il progetto del ricevitore ha seguito la scheda Zybo 7Z-20 mentre il trasmettitore ha seguito la scheda Z7-10. Gli FPGA sulle schede sono diversi, quindi… fai attenzione.

Ecco i passaggi per creare il blocco di progettazione del ricevitore:

-

Aggiungi i seguenti blocchi IP al tuo progetto:

- Controllore di temporizzazione

- AXI4-Stream su uscita video

- RGB a DVI

- AXI VDMA

- AXI GPIO

- Sistema di elaborazione

- Procedura guidata dell'orologio

- Costante (VDD impostato su 1)

- Segui lo stesso schema per configurare questi blocchi come trasmettitore. Le immagini per le notevoli differenze nella configurazione sono state incluse qui. Gli altri rimangono gli stessi del trasmettitore.

- Configurare il VDMA per questo progetto come solo canale di lettura. Disabilita il canale di scrittura.

-

La procedura guidata dell'orologio deve essere configurata per le seguenti uscite:

- clk_out1: 75 MHz (orologio pixel)

- clk_out2: 150 MHz (orologio in streaming)

- clk_out3: 50 MHz (clock axi-lite)

- Collega i blocchi video come mostrato nell'immagine del design del blocco RX.

- Quindi eseguire l'automazione della connessione, che aggiungerà i blocchi AXI Interconnect, AXI SmartConnect e System Reset e tenterà di effettuare le connessioni appropriate. Vai lentamente qui per assicurarti che non esegua connessioni indesiderate.

- Rendi l'orologio HDMI TMDS e i pin dati esterni sul blocco rgb2dvi

- Non c'è bisogno di segnale hot plug su questo design.

Passaggio 3: configurazione del driver VDMA

L'impostazione per i diversi blocchi configurati tramite l'interfaccia AXI-Lite viene eseguita al meglio utilizzando i progetti demo inclusi con il BSP come riferimento. Dopo aver esportato l'hardware di progettazione e aver avviato l'SDK da Vivado, ti consigliamo di aggiungere un nuovo pacchetto di supporto della scheda e includere la libreria lwip202 nella finestra delle impostazioni BSP. Apri il file system.mss dal BSP e vedrai i driver periferici presenti dal design del tuo blocco. L'opzione "Importa esempi" consente di importare progetti demo che utilizzano queste periferiche e quindi mostrarti come configurarli nel software utilizzando i driver Xilinx disponibili (vedi immagine allegata).

Questo era il metodo utilizzato per configurare VDMA, Timer & Interrupt e GPIO. Il codice sorgente sia per la trasmissione che per la ricezione è stato incluso qui. Le differenze riguardano quasi esclusivamente main.c.

***NOTA: poiché il sistema non è completamente funzionante al momento della stesura di questo tutorial, il codice sorgente in questa sezione non include il codice della rete wireless. Diversi bug devono essere risolti a seguito della combinazione dei progetti di trasmissione/ricezione del core video con i progetti di trasmissione/ricezione della rete. Pertanto questo tutorial li tratta separatamente per il momento.***

Funzione gestore interrupt TX (IRQHandler)

Questa funzione legge i codici grigi forniti dai VDMA di lettura e scrittura tramite i blocchi GPIO. I codici grigi vengono convertiti in decimali e utilizzati per selezionare la posizione di memoria di base del frame del frame corrente. Il frame copiato è il frame precedente a quello in cui viene scritto dal VDMA (ad esempio, se il VDMA sta scrivendo sul frame 2, copiamo il frame 1; se scrivendo sul frame 0, eseguiamo il wrapping e leggiamo dal frame 2).

La funzione acquisisce solo ogni sesto fotogramma per ridurre la frequenza dei fotogrammi a 10 Hz anziché a 60 Hz. Il limite superiore della rete è 300 Mbps. A 10 frame al secondo è richiesta una larghezza di banda di 221.2 Mbps.

Commentare/non commentare due righe in questa funzione consentirà all'utente di passare alla modalità passante HDMI per scopi di debug/test (il codice è commentato per indicare le righe appropriate). Attualmente copia il frame in una posizione di memoria utilizzata dal codice ethernet.

Funzione gestore interrupt RX (IRQHandler)

Questa funzione è molto simile alla funzione TX, ma copia da un FIFO a 2 buffer utilizzato dall'ethernet per scrivere i dati in ingresso. Il codice ethernet indica su quale frame viene scritto della FIFO, i dati vengono copiati dal frame opposto. I dati vengono copiati nel frame direttamente dietro a quello letto dal VDMA per evitare strappi.

Passaggio 4: configurazione della rete nanorouter

Per creare una rete utilizzando i nanorouter TPlink, accendili singolarmente e connettiti all'SSID wifi predefinito per i dispositivi. Maggiori informazioni sulle impostazioni di configurazione per questo particolare dispositivo possono essere trovate attraverso il manuale utente del dispositivo.

Imposta uno dei dispositivi come punto di accesso, questo fungerà da connessione primaria per la rete. Assicurati di nominare la rete e prendere nota del nome e disabilitare DHCP (non vogliamo che il router configuri gli indirizzi IP in modo dinamico, vogliamo che le schede Zybo del trasmettitore e del ricevitore impostino i loro indirizzi IP in modo che siano coerenti). Dopo la configurazione, assicurati che il dispositivo si riavvii e stabilisca questa rete.

Configura l'altro dispositivo come client e assicurati che si connetta all'SSID di rete configurato con il primo nanorouter. Ancora una volta, assicurati che DHCP sia disabilitato per il client.

Una volta che il client ha terminato e riavviato, dovrebbe connettersi al nanorouter del punto di accesso (in caso contrario, è probabile che ci sia un problema nella configurazione di uno dei dispositivi). Noterai che la luce LED sul client sarà fissa una volta connesso all'access point.

Il LED del nanorouter del punto di accesso probabilmente continuerà a lampeggiare a questo punto, va bene! La luce lampeggiante significa che non è connesso a un altro dispositivo dalla sua porta ethernet e, una volta connesso a uno Zybo configurato, il LED rimarrà fisso indicando una connessione di rete riuscita.

Ora che abbiamo configurato i nostri nanorouter, abbiamo una rete wireless che ci permetterà di comunicare. Una nota importante è che il nostro metodo di configurazione per i nanorouter (come access point e client) ci consente di comunicare dalla scheda Zybo trasmittente alla scheda Zybo ricevente come se i due fossero collegati con un unico cavo ethernet. Ciò rende la nostra configurazione di rete meno difficile, poiché l'alternativa probabilmente includerebbe la configurazione delle schede Zybo per connettersi esplicitamente al server insieme alla connessione prevista.

Una volta che entrambi i dispositivi sono stati configurati, i nanorouter sono configurati e pronti per essere implementati nella tua rete WIDI. Non esiste un accoppiamento specifico tra i nanorouter e le schede Zybo, poiché sia il punto di accesso che il client funzioneranno sia per il dispositivo di trasmissione che di ricezione.

Passaggio 5: configurazione del sistema di elaborazione Zynq per la trasmissione dei dati tramite Ethernet

Per trasmettere i dati HDMI da una scheda Zybo all'altra, dobbiamo incorporare un protocollo Ethernet nel nostro driver VDMA. Il nostro obiettivo qui è trasmettere singoli fotogrammi video attraverso la periferica Ethernet nel sistema di elaborazione, a una velocità impostata coerente con la larghezza di banda della nostra rete. Per il nostro progetto, abbiamo utilizzato TCP fornito dall'API LwIP bare metal. Poiché entrambi i membri del progetto sono relativamente inesperti con le utilità di rete, questa scelta è stata fatta senza riconoscere pienamente le implicazioni ei vincoli coinvolti con TCP. Il problema principale di questa implementazione era la larghezza di banda limitata e il fatto che in realtà non fosse progettata per lo scopo di trasferire volumi elevati di dati. Soluzioni alternative per sostituire TCP e migliorarlo in questo progetto verranno discusse più avanti.

Una breve descrizione di TCP con LwIP: I dati vengono inviati sulla rete in pacchetti di dimensioni tcp_mss (dimensione massima del segmento TCP), che generalmente è di 1460 byte. La chiamata a tcp_write richiederà alcuni dati a cui fa riferimento un puntatore e configurerà pbufs (packet buffer) per contenere i dati e fornire una struttura per le operazioni TCP. La quantità massima di dati che possono essere accodati in una volta è impostata come tcp_snd_buf (spazio buffer mittente TCP). Poiché questo parametro è un numero a 16 bit, siamo limitati a una dimensione del buffer di invio di 59695 byte (è necessario un riempimento nel buffer di invio). Una volta che i dati sono stati messi in coda, viene chiamato tcp_output per iniziare a trasmettere i dati. Prima di inviare il successivo segmento di dati, è imperativo che tutti i pacchetti precedenti siano stati trasmessi con successo. Questo processo viene eseguito utilizzando la funzione recv_callback, poiché questa è la funzione che viene chiamata quando il riconoscimento viene visualizzato dal destinatario.

L'utilizzo dei progetti di esempio in Vivado SDK è molto utile per imparare come funziona LwIP TCP ed è un buon punto di partenza per iniziare un nuovo progetto.

La procedura per il dispositivo trasmittente WiDi è la seguente:

- Inizializzare la rete TCP utilizzando le chiamate alla funzione del driver LWIP bare metal.

- Specificare le funzioni di callback necessarie per le operazioni di rete.

- Connettiti al ricevitore WiDi collegandoti al suo indirizzo IP e alla sua porta (la nostra configurazione: l'IP del ricevitore è 192.168.0.9, connettiti alla porta 7).

- Quando il timer del driver VDMA scade, inserire l'ISR TX.

- Determinare il frame buffer corrente a cui accedere in base al codice gray VDMA

- Metti in coda il primo segmento di dati nel buffer di invio TCP

- Emetti i dati e aggiorna le variabili locali per tenere traccia di quanti dati sono stati inviati del frame corrente.

- Al raggiungimento della richiamata ricevuta (chiamata di funzione effettuata dopo che il trasmettitore ha ricevuto un riconoscimento del recupero dei dati), accodare il successivo segmento di dati.

- Ripetere i passaggi 7 e 8 finché non è stato inviato l'intero frame.

- Tornare allo stato di inattività per attendere il successivo interrupt del timer per indicare che un nuovo frame è pronto (Torna al passaggio 4).

Assicurati di configurare le impostazioni LwIP del pacchetto di supporto della scheda come mostrato nell'immagine sopra. Tutti i valori sono predefiniti tranne tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Si noti inoltre che il debug dettagliato può essere ottenuto modificando i parametri BSP per il gruppo debug_options.

Passaggio 6: configurazione del sistema di elaborazione Zynq per la ricezione dei dati tramite Ethernet

La scheda di sviluppo Zybo che fungerà da ricevitore wireless funzionerà in modo simile al dispositivo di trasmissione. Le impostazioni del pacchetto di supporto della scheda per LwIP saranno identiche a quelle del passaggio precedente.

Il dispositivo acquisirà pacchetti contenenti i segmenti di frame video dal nanorouter e copierà i dati di frame video nello spazio del buffer di frame triplo per il VDMA ricevente. Per evitare la sovrascrittura dei dati, viene utilizzato un doppio buffer di dati (che chiameremo buffer di rete) quando si raccolgono dati dal nanorouter, in modo che il traffico di rete possa continuare a fluire mentre il precedente fotogramma video completo viene copiato nel tampone VDMA.

La procedura per il dispositivo di ricezione WiDi richiede due attività, una delle quali è la ricezione di dati ethernet e l'altra è la copia di frame video dal buffer di rete al triplo frame buffer del VDMA.

Compito di ricezione Ethernet:

- Inizializzare la rete TCP utilizzando le chiamate alla funzione del driver LWIP bare metal (configurazione con indirizzo IP a cui si connetterà il trasmettitore, 192.168.0.9 nel nostro)

- Specificare le funzioni di callback necessarie per le operazioni di rete.

- Al pacchetto Ethernet ricevuto, copiare i dati del pacchetto nel buffer di rete corrente, aumentare i dati accumulati correnti.

- Se il pacchetto riempie il buffer del frame di rete, continuare con i passaggi 5 e 6. Altrimenti, tornare al passaggio 3 per questa attività.

- segnala che l'attività VDMA triple frame buffer deve copiare dal buffer di rete appena terminato.

- Passa all'altro buffer di rete e continua a raccogliere dati tramite Ethernet.

- Inattivo fino alla ricezione di un nuovo pacchetto ethernet (passo 3).

Copia il buffer di rete nel triplo frame buffer VDMA:

- Quando il timer del driver VDMA scade, inserire l'RX ISR.

- Determinare il frame buffer corrente a cui accedere in base al codice gray VDMA.

- Determina quale buffer di rete verrà copiato nel buffer VDMA e copia quei dati

Passaggio 7: collega le tue schede Zybo alla sorgente HDMI e al dissipatore HDMI

Ora collega i cavi hdmi sia per il ricevitore che per il trasmettitore, programma gli FPGA ed esegui il sistema di elaborazione. Il frame rate sarà probabilmente molto lento, a causa dell'enorme sovraccarico nell'operazione LwIP e della larghezza di banda limitata. In caso di problemi, connettersi tramite UART e provare a identificare eventuali avvisi o errori.

Passaggio 8: idee alternative per il miglioramento

Un grosso problema per questo progetto era la quantità di dati necessari per l'invio tramite Wi-Fi. Questo era previsto, tuttavia abbiamo sottovalutato l'impatto che ciò avrebbe avuto e si è tradotto in più di una raffica di immagini su uno schermo piuttosto che su un feed video. Ci sono diversi modi per migliorare questo progetto:

- Compressione video in tempo reale. La compressione del feed video in ingresso fotogramma per fotogramma ridurrebbe notevolmente la quantità di dati necessari per l'invio in rete. Idealmente questo dovrebbe essere fatto nell'hardware (che non è un compito facile), o potrebbe essere fatto nel software utilizzando l'altro core ARM per eseguire un algoritmo di compressione (questo richiederebbe ulteriori analisi per garantire che i tempi funzionino). Ci sono alcuni componenti di compressione video in tempo reale open source che abbiamo trovato sul web, ma la maggior parte sono IP.

- Implementazione del flusso Ethernet nell'hardware, piuttosto che nel software. C'era un sacco di sovraccarico a causa della mancanza di spazio disponibile per mettere in coda i dati in uscita nel trasmettitore, a causa della limitazione della dimensione del segmento. Un processo molto più efficiente consiste nell'utilizzare l'IP Ethernet AXI con un buffer FIFO o DMA per alimentare i dati al suo interno. Ciò ridurrebbe il bagaglio extra da LwIP TCP e consentirebbe un maggiore flusso di dati.

Passaggio 9: accessibilità

Il prodotto risultante di questo progetto WiDi dovrebbe essere una coppia di dispositivi completamente integrati e compatti che un utente potrebbe collegare a qualsiasi sorgente HDMI e quindi inviare il feed video a un display con funzionalità HDMI in modalità wireless. I dispositivi presenteranno il SoC Zynq-7000 che si trova sulla scheda di riferimento Zybo e incorporeranno l'hardware di rete trovato nei nano-router TP-Link. Idealmente, l'utente sarebbe in grado di controllare il modulo di trasmissione da una posizione discreta all'interno del sistema operativo di destinazione, con poca necessità di capacità tecniche significative.

Sicurezza e connettività

I dispositivi dovrebbero anche incorporare Transport Layer Security (TLS) e avere una capacità di connessione automatica limitata, entrambi per motivi di privacy. È intenzione dei progettisti rendere la connessione con un display tramite un'interfaccia wireless un'azione deliberata da parte dell'utente per evitare la trasmissione errata di materiale sensibile.

Stato attuale

Fino a questo punto, lo stato del progetto è ancora molto in corso. Affinché l'attuale utente finale possa trarre vantaggio da questo tutorial, deve avere una solida conoscenza tecnica della progettazione di sistemi embedded e dovrebbe avere una certa familiarità con l'hardware programmabile e il software embedded che lavorano insieme.

I dati inviati sulla rete non sono crittografati a questo punto e si presume che siano una trasmissione grezza di pacchetti TCP/IP.

Il progetto video core è stato testato con successo sia per la trasmissione che per la ricezione. D'altra parte, è stata stabilita la connessione wireless tra due schede zybo e i dati del frame di prova sono stati inviati con successo. È ancora necessario, tuttavia, combinare il codice di rete a ciascun progetto core video e testare la trasmissione dei fotogrammi video effettivi.

Consigliato:

Scheda di sviluppo ESP32 fai da te - ESPer: 5 passaggi (con immagini)

Scheda di sviluppo ESP32 fai-da-te - ESPer: Di recente ho letto di molti IoT (Internet of Things) e fidati di me, non vedevo l'ora di testare uno di questi meravigliosi dispositivi, con la possibilità di connettersi a Internet, me stesso e mettere le mani sul lavoro. Per fortuna l'occasione a

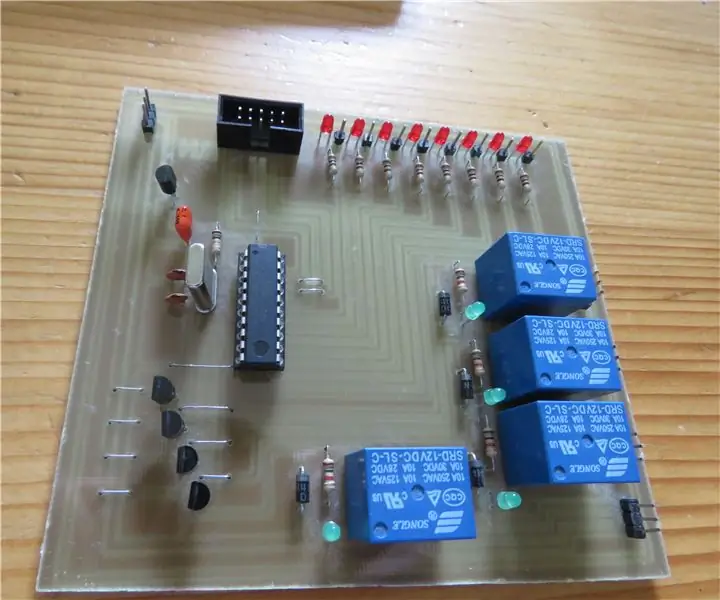

Crea la tua scheda di sviluppo con microcontrollore: 3 passaggi (con immagini)

Crea la tua scheda di sviluppo con microcontrollore: hai mai desiderato creare la tua scheda di sviluppo con microcontrollore e non sapevi come. In questo tutorial ti mostrerò come realizzarla. Tutto ciò di cui hai bisogno è conoscenza dell'elettronica, progettazione di circuiti e programmazione. Se hai qualche missione

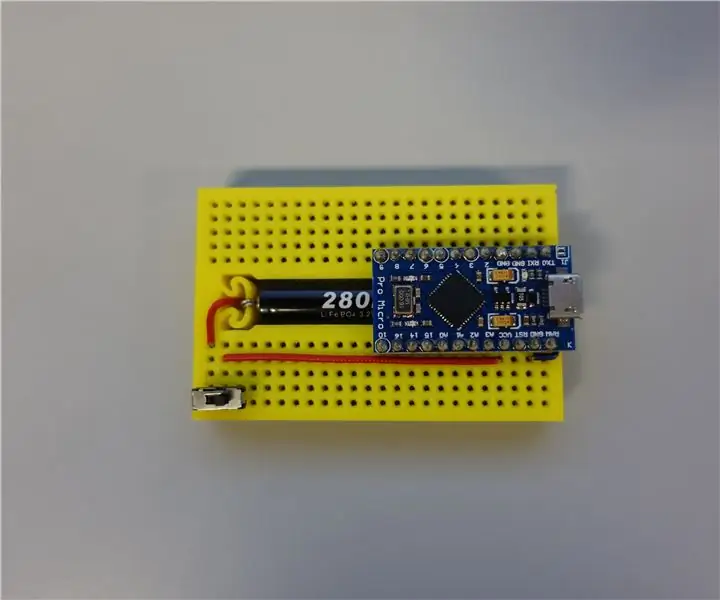

Breadboard della scheda di sviluppo: 12 passaggi (con immagini)

Breadboard della scheda di sviluppo: questo Instructables mostra come creare una breadboard su misura per la scheda di sviluppo

Quadricottero che utilizza la scheda Zybo Zynq-7000: 5 passaggi

Quadricottero che utilizza la scheda Zybo Zynq-7000: prima di iniziare, ecco alcune cose che desideri per il progetto: Elenco delle parti 1 x scheda Digilent Zybo Zynq-7000 1 x telaio quadricottero in grado di montare Zybo (file Adobe Illustrator per il taglio laser allegato) 4 x Turnigy D3530/ 14 Motori Brushless 1100KV 4x

UDuino: scheda di sviluppo compatibile con Arduino a bassissimo costo: 7 passaggi (con immagini)

UDuino: scheda di sviluppo compatibile con Arduino a bassissimo costo: le schede Arduino sono ottime per la prototipazione. Tuttavia, diventano piuttosto costosi quando si hanno più progetti simultanei o sono necessarie molte schede controller per un progetto più ampio. Ci sono alcune ottime alternative più economiche (Boarduino, Freeduino) ma