Sommario:

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:03.

- Ultima modifica 2025-01-23 14:49.

So cosa ne pensi: "Eh? Ci sono molti Instructables su come utilizzare i microcontrollori per misurare la frequenza del segnale. Sbadiglio". Ma aspetta, c'è una novità in questo: descrivo un metodo per misurare frequenze molto più alte di quelle che un microcontrollore (MCU) può sopportare e il ciclo di lavoro del segnale - tutto allo stesso tempo!

La gamma di frequenza del dispositivo va da ~43 Hz a ~450 kHz, mentre il ciclo di lavoro varia dall'1% al 99%.

Mi spiego la parte "può sopportare": un MCU misura il periodo di un segnale ad onda quadra, T, tracciando il tempo tra due eventi di transizione successivi. Ad esempio, la tensione da bassa ad alta salta su uno dei suoi pin I/O. Lo fa contando il numero di impulsi del proprio orologio interno. Ingenuamente, il limite superiore per le frequenze misurate dovrebbe obbedire al teorema di campionamento di Nyqvist-Shannon; cioè, sarebbe all'incirca uguale alla metà della frequenza di clock dell'MCU. In realtà il limite è molto, molto più basso, perché l'MCU deve eseguire il codice per gestire gli interrupt, salvare le variabili, fare operazioni aritmetiche, visualizzare i risultati, ecc. Nei miei esperimenti con un MCU a 48 MHz il numero minimo di cicli di clock tra le transizioni misurabili era circa 106. Quindi, il limite superiore della gamma di frequenze misurabili in questo caso sarebbe 48, 000 / 212 / 2 = 226,4 kHz.

Mentre l'MCU misura il periodo del segnale, può anche determinare la sua larghezza di impulso, P: il tempo in cui la tensione del segnale rimane alta. In altre parole, il tempo tra le transizioni da basso ad alto e da alto a basso. Il ciclo di lavoro del segnale viene quindi definito come la seguente percentuale:

Dazio = 100% * P / T

Proprio come nel caso della frequenza, esiste un limite pratico alla larghezza dell'impulso. Utilizzando l'esempio precedente, 106 cicli di clock limiterebbero la larghezza dell'impulso a non meno di 2,21 microsecondi. Oppure, non meno del 50% a 226,4 kHz.

Uno dei modi per aumentare il limite di frequenza superiore dei segnali ad onda quadra è l'applicazione di divisori digitali che utilizzano flip-flop. Dividere la frequenza di ingresso per n estenderebbe l'intervallo superiore misurabile n volte. Questa è un'ottima notizia, i divisori digitali hanno un difetto fondamentale: il segnale diviso perde le informazioni sulla larghezza dell'impulso (e sul ciclo di lavoro)! A causa del modo in cui funzionano i divisori, la loro uscita ha sempre un ciclo di lavoro del 50%. Peccato…

Nelle pagine seguenti, invece, mostrerò come dividere digitalmente la frequenza e preservare l'ampiezza dell'impulso originale permettendomi di misurare segnali ben oltre i limiti imposti dal conteggio diretto.

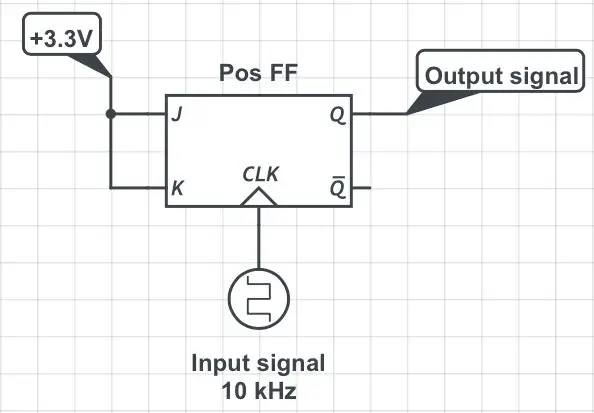

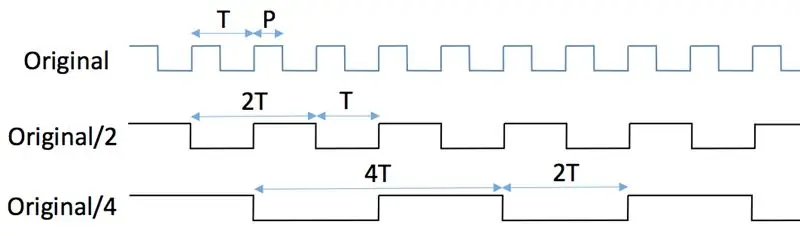

Fase 1: Divisione di frequenza digitale

I tradizionali divisori di frequenza digitali utilizzano flip-flop; questo tutorial spiega bene i principi su come costruire i divisori usando le infradito JK standard. Questo risolve il problema delle frequenze di ingresso troppo alte per l'MCU, ma ha un grosso inconveniente: il segnale diviso ha un ciclo di lavoro del 50% indipendentemente dal dovere del segnale di ingresso! Per capire perché è così, guarda le prime due cifre. Il segnale originale con periodo T e larghezza di impulso P viene immesso nel pin di clock di un flip-flop JK mentre i suoi pin J e K sono sempre mantenuti alti (prima figura). La logica a 3,3 V è sempre presunta. Supponiamo che il flip-flop venga attivato dal fronte positivo (cioè ascendente) del clock. In queste condizioni, ogni volta che il pin di clock passa da basso ad alto, si verificano cambiamenti di stato del pin di uscita (singoli "flip" e "flop"). La transizione da alto a basso del clock (cioè il fronte negativo) viene completamente ignorata. Vedi la seconda figura. Il pin di uscita, Q, emette un segnale il cui periodo è il doppio del periodo originale, cioè la sua frequenza è dimezzata. L'ampiezza dell'impulso dell'uscita è sempre uguale a T. Di conseguenza, l'ampiezza dell'impulso originale, P, viene persa.

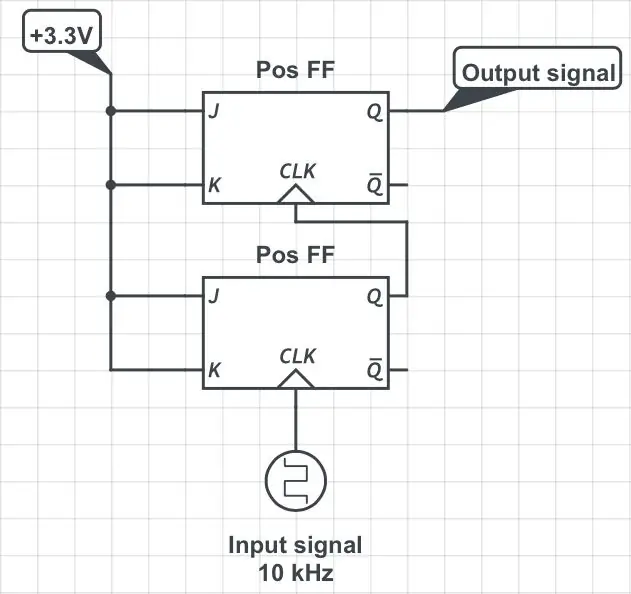

L'aggiunta di un altro flip-flop JK in una configurazione mostrata nella terza figura divide la frequenza originale per 4. L'aggiunta di più flip-flop nello stesso modo sequenziale divide la frequenza per le successive potenze di 2: 8, 16, 32, ecc.

Problema: come dividere la frequenza di un'onda quadra preservandone la larghezza dell'impulso?

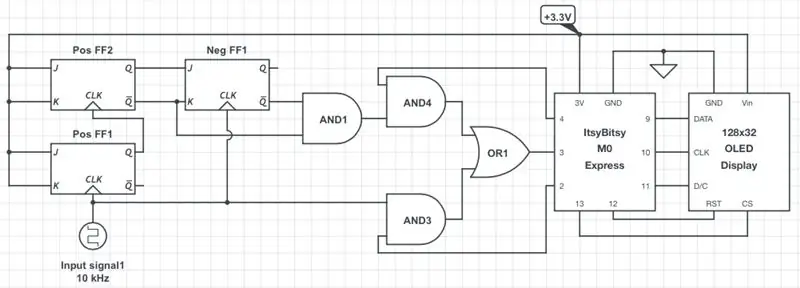

L'idea è di aggiungere correttamente un flip-flop JK innescato dal fronte negativo al mix. Chiamiamola "Neg FF"; vedi quarta figura. Qui, "correttamente" significa che i pin J e K del nuovo flip-flop sono legati rispettivamente ai pin di uscita Q e Qbar del divisore per 4 ("Pos FF") illustrato nella figura precedente. (Qui, "bar" è la barra orizzontale sopra il simbolo Q che indica la negazione logica.) Per vedere cosa si ottiene, dai un'occhiata alla tabella delle funzioni di "Neg FF" nella quinta figura: pin di uscita di Neg, Q e Qbar, rispecchiano lo stato dei suoi pin di input, J e K, rispettivamente. Ciò significa che rispecchiano lo stato di Q e Qbar di Pos. Ma l'azione del flip-flop del Neg deve attendere il fronte negativo del segnale originale, che arriva al momento P dopo il fronte positivo. Ah!

Le forme d'onda risultanti sono illustrate nella sesta figura. "Pos Q" emette il segnale a 1/4 di frequenza, "Pos Qbar" è l'inverso, "Neg Q" segue "Pos Q" spostato della larghezza dell'impulso P e "Neg Qbar" è il suo inverso. È possibile verificare che l'AND logico di "Pos Qbar" e "Neg Q" produce un treno di impulsi caratterizzato dalla larghezza dell'impulso originale P e 1/4 della frequenza. Bingo!

All'inizio ho usato esattamente questo segnale di uscita per alimentare l'MCU. Tuttavia, si è rivelato problematico per larghezze di impulso molto brevi a causa della limitazione di 106 cicli dell'MCU menzionata nell'Introduzione. Ho risolto questo piccolo problema selezionando un altro output: "Pos Qbar" AND "Neg Qbar" invece. Uno sguardo alle forme d'onda dovrebbe convincerti che l'ampiezza dell'impulso di questa particolare forma d'onda, P', varia tra T e 2T invece dell'intervallo (0, T) per P. La P può essere facilmente recuperata da P' tramite:

P = 2T - P'

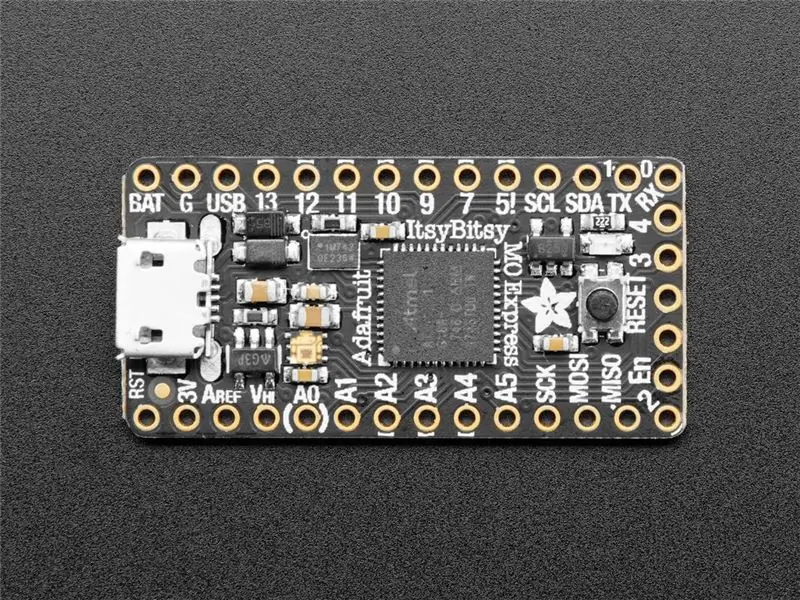

Passaggio 2: hardware consigliato

Mi piace davvero il nuovo arrivato relativamente agli hobbisti elettronici: gli MCU Atmel SAM D21 basati sul processore ARM Cortex M0+ a 32 bit che opera a una frequenza di clock di 48 MHz, molto più alta dei vecchi Atmel. Per questo progetto ho acquistato:

- Scheda MCU ItsyBitsy M0 Express di Adafruit

- Mi è capitato di avere una batteria LiPo ricaricabile di Adafruit

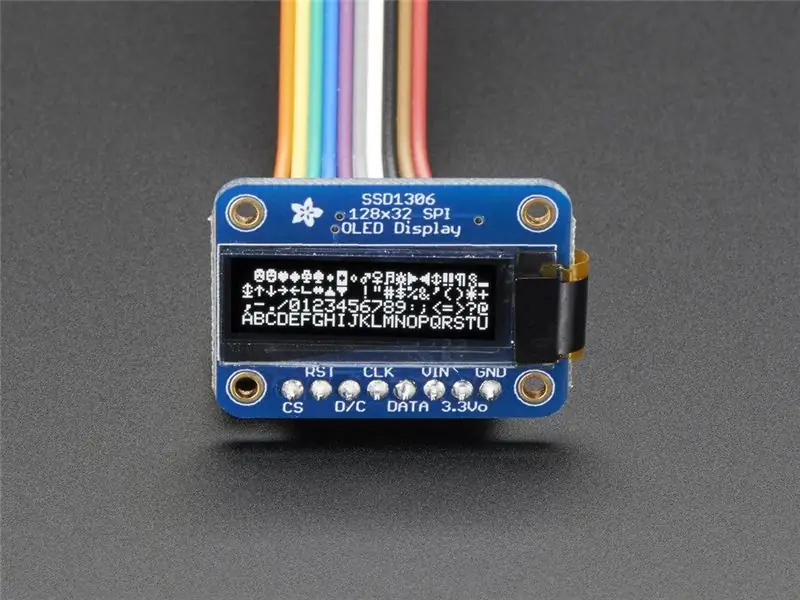

- Display OLED SPI monocromatico 128x32 (avete indovinato: Adafruit)

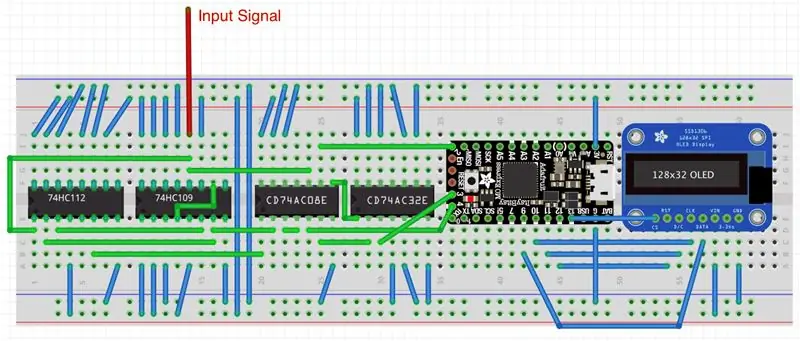

- Doppio flip-flop JK con trigger sul fronte positivo SN74HC109 di Texas Instruments

- Doppio flip-flop JK con trigger sul fronte negativo SN74HC112 di Texas Instruments

- Quadruplo AND gate CD74AC08E di Texas Instruments

- Cancello OR quadruplo CD74AC32E di Texas Instruments

Passaggio 3: il circuito

La prima figura mostra uno schema semplificato del frequenzimetro/duty meter. La logica CMOS a 3,3 V è sempre stata assunta. Di conseguenza, l'ampiezza dell'onda quadra in ingresso deve essere compresa tra i corrispondenti VIH livello (cioè 2 V) e 3,3 V. In caso contrario, è necessario aumentarlo o ridurlo di conseguenza. Nella maggior parte dei casi sarebbe sufficiente un semplice partitore di tensione. Se vuoi progettare la tua versione del misuratore a un livello logico diverso, devi utilizzare un altro micro controller (MCU), una batteria e un display che funzionino al livello desiderato. Le porte logiche e i flip-flop utilizzati in questo progetto funzionano con livelli logici compresi tra 2 V e 6 V e dovrebbero essere OK nella maggior parte dei casi.

Come mostrato, l'MCU ItsyBitsy utilizza i pin 9-13 per comunicare con il display tramite il protocollo SPI del software. Il pin 3V fornisce alimentazione all'intero circuito. Il pin 3 dell'ingresso digitale accetta il segnale analizzato, mentre i pin 2 e 4 controllano la sorgente del segnale: segnale diretto che arriva attraverso il gate AND3 (basse frequenze di ingresso) o segnale diviso per 4 attraverso il gate AND4 (frequenze di ingresso alte) come descritto nel passaggio 2 Il codice, discusso nel passaggio successivo, rileva automaticamente la gamma di frequenza in ingresso e commuta opportunamente la sorgente del segnale.

Lo schema non mostra la vera complessità delle connessioni dei chip digitali. La seconda immagine mostra come apparirebbe il progetto su una breadboard. Il segnale di ingresso arriva attraverso un filo rosso al pin 2CLK del flip-flop a doppio fronte positivo. ATTENZIONE: Normalmente, tutti i pin J e K di questo flip-flop dovrebbero essere tenuti alti, ma SN74HC109 in particolare presenta il pin Kbar, un pin K invertito. Quindi, questo pin deve essere messo a terra! Il primo flip-flop con fronte negativo in SN74HC112 ha i suoi pin 1K e 1J collegati ai pin 1Q e 1Qbar di SN74HC109. Il secondo flip-flop in SN74HC112 non è utilizzato e i suoi pin di ingresso (2K, 2J, 2CLRbar) sono collegati a terra. Tutti gli altri pin aggiuntivi PREbar (preimpostato) e CLRbar (clear) in tutti i flip-flop devono essere collegati al livello logico alto. I pin di clock e di uscita non utilizzati vengono lasciati scollegati. Allo stesso modo, i pin di ingresso inutilizzati in tutte le porte sono messi a terra, mentre i pin di uscita non utilizzati vengono lasciati scollegati. Come ho discusso nel mio Instructable "Invisible Killer of the Phone Ring", la messa a terra dei pin di ingresso inutilizzati dei chip logici elimina le oscillazioni casuali e consente di risparmiare la carica della batteria.

Passaggio 4: il codice e la misurazione delle basse frequenze

Naturalmente, tutta l'azione avviene nel codice collegato di seguito. Quando l'ingresso in ingresso sul pin 3 passa da digitale basso ad alto, l'MCU inizia a contare gli impulsi del suo clock interno a 48 MHz. Annota il momento della transizione da alto a basso e continua il conteggio fino al successivo passaggio da basso a alto, quando riavvia di nuovo l'intero processo. Il primo conteggio rappresenta la durata dell'impulso, mentre l'intero conteggio rappresenta il periodo del segnale. E questo è l'intero segreto.

La CPU rileva queste transizioni tramite interrupt hardware. Il SAMD21 ha diversi orologi; il mio codice usa uno TC3. Inizialmente, ho iniziato leggendo il foglio dati dell'M0, facendo un grande sforzo nella codifica del gestore di interrupt, ma presto ho scoperto un codice molto correlato nei post del forum Arduino degli utenti electro_95, MartinL e Rucus il cui contributo è debitamente riconosciuto. Ho incorporato e modificato il loro codice combinato nel mio; risparmiandomi un sacco di tempo!

Come accennato in precedenza, la risoluzione del segnale è limitata da ~106 cicli della CPU per eseguire il codice tra gli interrupt. La divisione digitale con conservazione della larghezza d'impulso si occupa delle alte frequenze. Le basse frequenze, d'altra parte, rappresentano un'altra sfida: poiché il contatore di clock TC3 è lungo 16 bit, va in overflow dopo aver superato il limite di 65, 536 conteggi. Si può gestire questa situazione aggiungendo un interrupt di overflow, ma si è scelta una soluzione diversa: TC3 può utilizzare un clock della CPU prescalato (cioè suddiviso dal software) invece di quello hardware a 48 MHz. Pertanto, se il periodo del segnale si avvicina al limite di overflow, il codice può indicare a TC3 di utilizzare conteggi a 24 MHz per il periodo successivo e, voilà, il contatore scende al di sotto di 32, 768 conteggi. Per frequenze ancora più basse, il TC3 può essere istruito a contare impulsi a 12 MHz, ecc. Il prescaler appropriato viene determinato automaticamente in base alla frequenza del segnale, con isteresi, per mantenere il contatore TC3 entro il limite di overflow. Di conseguenza, l'estremità inferiore della gamma del dispositivo è di circa 43 Hz.

Puoi eseguire il fork del codice e utilizzarlo nel tuo progetto, ma ti preghiamo di menzionarne la fonte quando pubblichi i risultati.

Link al codice.

Consigliato:

Misurare la frequenza cardiaca è a portata di mano: approccio fotopletismografico per determinare la frequenza cardiaca: 7 passaggi

La misurazione della frequenza cardiaca è a portata di dito: approccio fotopletismografico alla determinazione della frequenza cardiaca: un fotopletismografo (PPG) è una tecnica ottica semplice ed economica che viene spesso utilizzata per rilevare i cambiamenti nel volume del sangue in un letto microvascolare di tessuto. Viene utilizzato principalmente in modo non invasivo per effettuare misurazioni sulla superficie della pelle, in genere

Come realizzare un drone utilizzando Arduino UNO - Crea un quadricottero usando il microcontrollore: 8 passaggi (con immagini)

Come realizzare un drone utilizzando Arduino UNO | Crea un quadricottero usando il microcontrollore: introduzioneVisita il mio canale YoutubeUn drone è un gadget (prodotto) molto costoso da acquistare. In questo post ho intenzione di discutere, come lo faccio a buon mercato?? E come puoi creare il tuo come questo a un prezzo economico … Bene in India tutti i materiali (motori, ESC

Configurazione dei fusibili del microcontrollore AVR. Creazione e caricamento nella memoria flash del microcontrollore del programma di lampeggio dei LED.: 5 passaggi

Configurazione dei fusibili del microcontrollore AVR. Creazione e caricamento nella memoria flash del microcontrollore del LED lampeggiante Program.: In questo caso creeremo un semplice programma in codice C e lo masterizzeremo nella memoria del microcontrollore. Scriveremo il nostro programma e compileremo il file esadecimale, utilizzando Atmel Studio come piattaforma di sviluppo integrata. Configurare il fusibile bi

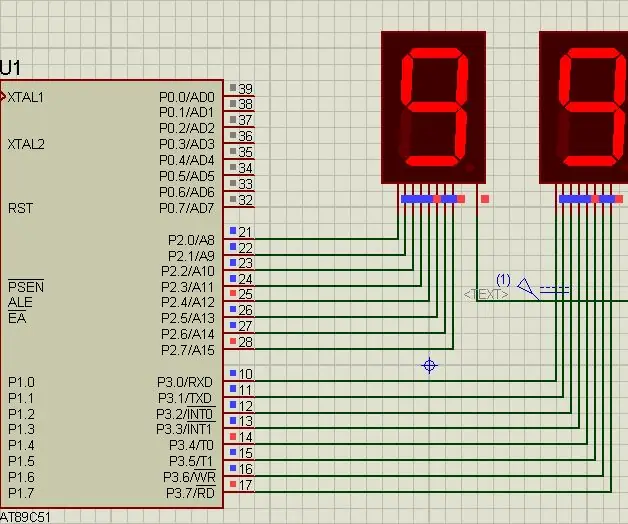

Come contare da 0 a 99 utilizzando il microcontrollore 8051 con display a 7 segmenti: 5 passaggi (con immagini)

Come contare da 0 a 99 utilizzando il microcontrollore 8051 con display a 7 segmenti: Ciao a tutti, In questo tutorial vi parleremo di come contare da 0 a 99 utilizzando due display a 7 segmenti

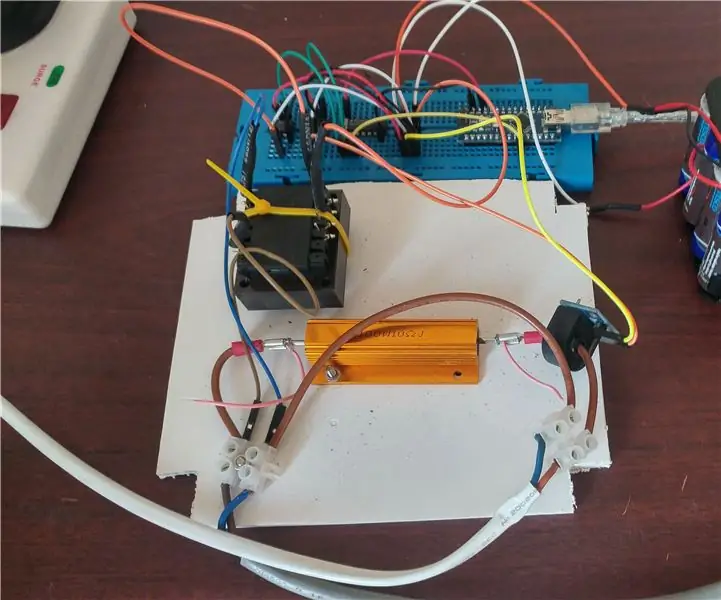

Come misurare il fattore di potenza CA utilizzando Arduino: 4 passaggi

Come misurare il fattore di potenza CA utilizzando Arduino: Ciao a tutti! Questa è la mia terza istruzione, spero che tu la trovi informativa :-) Questa sarà una guida su come eseguire una misurazione di base del fattore di potenza utilizzando un Arduino. Prima di iniziare ci sono alcune cose da tenere a mente: funzionerà SOLO con