Sommario:

- Passaggio 1: diagramma a blocchi

- Passaggio 2: principio di funzionamento

- Passaggio 3: implementazione della logica

- Passaggio 4: risoluzione dello stallo

- Passaggio 5: configurazione del dispositivo - Circuito Matrix0

- Passaggio 6: configurazione del dispositivo - Logica di clock SPI

- Passaggio 7: configurazione del dispositivo - Proprietà dei componenti Matrix0

- Passaggio 8: configurazione del dispositivo - Circuito Matrix1

- Passaggio 9: configurazione del dispositivo - contatore binario a 3 bit

- Passaggio 10: configurazione del dispositivo - Logica di confronto a 3 bit

- Passaggio 11: configurazione del dispositivo - Logica di confronto digitale e registro temporaneo

- Passaggio 12: Configurazione del dispositivo - Proprietà dei componenti Matrix1

- Passaggio 13: risultati

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:01.

- Ultima modifica 2025-01-23 14:49.

I sistemi di controllo e i relativi dispositivi gestiscono più fonti di alimentazione, come linee di polarizzazione o batterie, e devono tracciare la linea più alta (o più bassa) di un determinato set.

Ad esempio, la commutazione del carico in un sistema alimentato a "multi batteria" richiede che il sistema monitori la tensione minima o massima tra l'array di batterie (max o min in funzione del particolare algoritmo di commutazione) e indirizza dinamicamente il carico al fonte più appropriata in tempo reale. In alternativa, il sistema potrebbe dover scollegare temporaneamente la batteria a basso voltaggio per una corretta ricarica.

Un altro esempio è il moderno sistema di energia solare, dove ogni pannello solare è dotato di un meccanismo tiltrotate e di un circuito di inseguimento solare (quest'ultimo fornisce le informazioni sulla posizione del sole per orientare il pannello). Con le informazioni sulla tensione massima, ogni posizione del pannello solare può essere messa a punto in base al pannello della stringa che effettivamente fornisce la tensione di uscita più alta, ottenendo così un livello superiore di ottimizzazione della potenza.

Esistono diverse marche di circuiti integrati commerciali (principalmente microcontrollori) che in linea di principio possono implementare un follower di tensione massima. Tuttavia, richiedono programmazione e sono meno convenienti di una soluzione a segnale misto. L'integrazione di un design Dialog GreenPAKTM può influenzare positivamente l'accessibilità, le dimensioni e la modularità del design. Questo design sfrutta il vantaggio di integrare circuiti analogici e digitali in un unico chip.

In questo Instructable, viene implementato il front-end analogico e la logica digitale necessari per implementare un rilevatore di tensione massima (o eventualmente minima) tra otto sorgenti distinte.

Per implementare il monitor di tensione max/min analogico a 8 canali viene utilizzato un SLG46620G.

Di seguito abbiamo descritto i passaggi necessari per capire come è stata programmata la soluzione per creare il monitor analogico di tensione max/min a 8 canali. Tuttavia, se desideri solo ottenere il risultato della programmazione, scarica il software GreenPAK per visualizzare il file di progettazione GreenPAK già completato. Collega il kit di sviluppo GreenPAK al tuo computer e premi il programma per creare il monitor analogico di tensione max/min a 8 canali.

Passaggio 1: diagramma a blocchi

La Figura 1 mostra il diagramma globale del sistema implementato.

Una stringa fino a 8 sorgenti a tensione variabile è multiplexata e interfacciata a un modulo ADC di GreenPAK collegato ad un design interno personalizzato in grado di selezionare la sorgente con la tensione più alta rispetto alle altre. La logica interna emette queste informazioni per la visualizzazione o l'ulteriore elaborazione.

Il design si basa sul prodotto GreenPAK SLG46620G, perché incorpora tutti i blocchi di costruzione analogici e digitali necessari per l'applicazione. In questa implementazione l'array viene scansionato per mezzo di un multiplexer analogico ADG508 pilotato direttamente dall'IC GreenPAK.

Le informazioni di uscita sono un numero digitale a 3 bit corrispondente al numero della sorgente di tensione alla massima tensione. Un modo diretto per ottenere queste informazioni è mostrare il numero tramite un display a 7 segmenti. Può essere facilmente realizzato interfacciando l'uscita digitale dell'SLG46620G a un driver display a 7 segmenti, come la soluzione GreenPAK descritta in Riferimento o a un comune IC 74LS47.

Il circuito presentato cerca la massima tensione. Per convertire il progetto in un rilevatore di tensione minima, è necessario aggiungere un semplice circuito di precondizionamento tra il multiplexer analogico e l'ingresso analogico GreenPAK, sottraendo l'uscita del multiplexer da una tensione di riferimento di 1 V.

Passaggio 2: principio di funzionamento

Il progetto mira a selezionare la sorgente con tensione massima, quindi viene eseguita una scansione su tutto l'array memorizzando l'ultimo valore massimo e confrontandolo con il valore successivo in ingresso (che appartiene alla sorgente di tensione successiva nella scansione).

Nel seguito faremo riferimento ad una sequenza di multiplexing completa lungo tutti gli ingressi come “scan” o “loop”.

Il confronto tra due valori non viene effettuato tramite componenti ACMP (tuttavia disponibili in SLG46620G), ma piuttosto tramite il modulo DCMP, una volta che i valori sono rispettivamente digitalizzati. Questa è una tecnica avanzata e raffinata affrontata per la prima volta in Reference.

La Figura 2 mostra come è strutturato SLG46620G per questo progetto.

Il segnale di ingresso analogico va all'ingresso ADC attraverso il componente PGA con un guadagno impostato di 1. Sono inoltre possibili varie impostazioni di guadagno per trovare la migliore corrispondenza con l'elettronica di condizionamento front-end dedicata alla mappatura delle tensioni di ingresso su 0-1 V gamma del modulo ADC GreenPAK.

L'ADC opera in modalità single-ended e converte il segnale analogico in un codice digitale a 8 bit, che viene quindi trasferito al modulo DCMP. Il codice digitale viene anche immesso nel blocco SPI, configurato come buffer ADC/FSM, in cui è possibile memorizzare un codice digitale e non cambierà fino a quando l'impulso successivo non arriva all'ingresso SPI CLK. Notare che un blocco logico dedicato pilota l'ingresso SPI CLK. Indagheremo su questa parte in seguito, poiché questa è la logica "centrale" responsabile del corretto funzionamento. Un nuovo codice digitale viene memorizzato nel modulo SPI solo se appartiene alla tensione di ingresso massima effettiva.

Il componente DCMP viene utilizzato per confrontare i dati ADC correnti con l'ultimo vincitore (ovvero l'ultimo massimo trovato) che viene memorizzato nel blocco SPI. Genererà un impulso all'uscita OUT+ quando i nuovi dati ADC sono maggiori di quelli precedenti. Usiamo il segnale OUT+ per aggiornare il blocco SPI con il nuovo vincitore.

Un segnale di clock globale guida le conversioni ADC e le temporizzazioni generali. Una volta eseguita una conversione, il segnale di uscita INT dell'ADC emette impulsi, coordinati nel tempo con l'uscita dati parallela dell'ADC. Usiamo l'uscita INT anche per incrementare un contatore binario a 3 bit, implementato dai DFF in Matrix1, che è utile per tre ragioni:

1. Le linee di uscita del contatore indirizzano il multiplexer analogico esterno, servendo così la successiva tensione di ingresso all'ADC;

2. Il conteggio viene congelato in un registro a 3 bit (implementato in Matrix1) per memorizzare il vincitore temporaneo durante una scansione;

3. Il conteggio viene decodificato per aggiornare un secondo registro a 3 bit (implementato in Matrix0) una volta completata la scansione.

Passaggio 3: implementazione della logica

Il modulo ADC fornisce in sequenza i dati convertiti di tutte le tensioni di ingresso, una dopo l'altra, indefinitamente. Una volta indirizzato il Multiplexer 0b111 (decimale 7), il contatore scende a 0b000 (decimale 0) iniziando così una nuova scansione delle tensioni di ingresso.

Durante la scansione, il segnale di uscita ADC INT viene generato quando l'uscita dati parallela è valida. Quando questo segnale pulsa, il multiplexer analogico deve passare all'ingresso successivo, fornendo al PGA la tensione corrispondente. Pertanto, l'uscita ADC INT è il segnale di clock diretto del contatore binario a 3 bit di Figura 2, la cui parola di uscita parallela a 3 bit indirizza direttamente il multiplexer analogico esterno ("V select" in Figura 1).

Facciamo ora riferimento a un esempio in cui le tensioni di ingresso dovrebbero avere le seguenti relazioni:

a) V0 < V1 < V2

b) V2 > V3, V4

c) V5 > V2

La figura 3 rappresenta i principali segnali coinvolti nel meccanismo di massima decisione.

Poiché i dati vengono infine sincronizzati nel registro del buffer SPI in modo sincrono con gli impulsi INT, esiste una finestra di confronto in cui il contenuto del buffer SPI viene confrontato con il successivo risultato della conversione ADC. Questa particolare temporizzazione determina la generazione di impulsi OUT+ all'uscita DCMP. Possiamo sfruttare questi impulsi per caricare nuovi valori nel registro del buffer SPI.

Come si evince dalla riga dati del buffer SPI della Figura precedente, il registro SPI contiene sempre, di volta in volta, il valore maggiore tra gli 8 ingressi e viene aggiornato solo quando viene rilevato un valore maggiore dal modulo DCMP (riferito al DCMP OUT+ linea di uscita del grafico, gli impulsi mancanti fanno sì che V2 rimanga agganciato nel registro fino al confronto con V5).

Passaggio 4: risoluzione dello stallo

Se la logica implementata fosse proprio quella sopra descritta, è chiaro che ci imbatteremmo in una situazione di stallo: il sistema è in grado di rilevare solo tensioni superiori a quella corrispondente a quanto memorizzato nel buffer register SPI.

Questo vale anche nel caso in cui questa tensione diminuisse e poi un altro ingresso, fino ad ora inferiore a quello, diventi il più alto: non verrebbe mai rilevato. Questa situazione è meglio spiegata in Figura 4 dove sono presenti solo 3 tensioni di ingresso per motivi di chiarezza.

Al momento dell'iterazione 2, V3 scende e V1 è la tensione massima effettiva. Ma il modulo DCMP non fornisce un impulso perché i dati memorizzati nel registro del buffer SPI (corrispondente a 0,6 V) sono maggiori di quelli corrispondenti a V1 (0,4 V).

Il sistema si comporta quindi come un cercatore massimo "assoluto" e non aggiorna l'output correttamente.

Un buon modo per superare questo problema è forzare il ricaricamento dei dati nello SPI Buffer Register quando il sistema completa un ciclo di polling completo di tutti i canali.

Infatti, se la tensione a quell'ingresso è ancora la più alta, non cambia nulla e il controllo va avanti in sicurezza (facendo riferimento alla Figura 4 sopra, questo è il caso delle Iterazioni di Loop 0 e 1). Se invece la tensione su quell'ingresso si abbassa per caso ad un valore minore di un altro ingresso, ricaricare il valore dà la possibilità al modulo DCMP di produrre un impulso OUT+ confrontandolo con il nuovo valore massimo (questo è il caso di iterazioni di loop 2 e 3).

Un pezzo di circuito logico è necessario per superare il problema. Deve generare un segnale di clock al componente SPI quando il loop raggiunge l'ingresso massimo effettivo, forzando così un ricaricamento della sua parola di dati aggiornata nel registro buffer SPI. Questo sarà discusso nelle Sezioni 7.2 e 7.6 di seguito.

Passaggio 5: configurazione del dispositivo - Circuito Matrix0

SLG46620G dispone di due blocchi Matrix, come illustrato nella Figura 2. Le figure seguenti mostrano le rispettive configurazioni del dispositivo.

La parte superiore del circuito è il “Loop Register” realizzato con 3 DFF (DFF0, DFF1 e DFF2). Viene aggiornato dopo ogni loop del multiplexer di ingresso per inviare ad un driver display a 7 segmenti il numero binario del “vincitore”, cioè l'ingresso con la tensione più alta nell'ultima scansione. Sia l'orologio dei DFF che i dati provengono dalla logica implementata in Matrix1 attraverso, rispettivamente, le porte P12, P13, P14 e P15.

La parte inferiore è il front end analogico con ingresso al Pin 8 e PGA con guadagno x1. L'uscita ADC INT va sia alla logica di clock di SPI che a Matrix1 tramite la porta P0, dove servirà come segnale di clock per il contatore implementato.

Le uscite dati parallele ADC e SPI sono rispettivamente etichettate NET11 e NET15 per essere collegate al componente DCMP in Matrix1.

Passaggio 6: configurazione del dispositivo - Logica di clock SPI

Come evidenziato in precedenza nella sezione "Implementazione logica", lo SPI Buffer Register viene aggiornato ogni volta che un confronto tra il valore attuale memorizzato e i nuovi dati di conversione ADC genera un impulso all'uscita DCMP OUT+.

L'integrità del segnale è assicurata se questo segnale è collegato in AND con l'uscita ADC INT. In questo modo si evitano picchi e falsi trigger.

Abbiamo anche sottolineato che per saltare le situazioni di deadlock, lo SPI Buffer deve essere aggiornato quando il loop raggiunge i dati effettivi del vincitore.

Tre segnali quindi sono in gioco per un corretto clock SPI:

1. Uscita ADC INT (LUT0-IN1)

2. Uscita DCMP OUT+ (LUT0-IN0 tramite porta P10)

3. Il conteggio è uguale al segnale Latch (LUT0-IN2 tramite la porta P11)

I primi due sono in AND ed entrambi in OR con quest'ultimo in LUT0, la cui implementazione è configurata come in Figura 6.

Passaggio 7: configurazione del dispositivo - Proprietà dei componenti Matrix0

Le Figure 7-10 mostrano le restanti finestre delle proprietà dei componenti appartenenti a Matrix0.

Passaggio 8: configurazione del dispositivo - Circuito Matrix1

Passaggio 9: configurazione del dispositivo - contatore binario a 3 bit

La parte superiore del circuito contiene elementi logici, principalmente un contatore binario a 3 bit sincronizzato dall'uscita ADC INT, come già discusso. Questo contatore è implementato con uno schema abbastanza “standard” mostrato nella Figura 12.

Questo contatore è realizzato nel nostro design tramite Flip-Flop DFF9, DFF10, DFF11 e INV1, LUT4, LUT8. L'uscita DFF9 è l'LSB mentre DFF11 è l'MSB come mostrato nella Figura 13.

LUT4 è configurato come XOR mentre LUT8 esegue la logica AND-XOR di Figura 12.

Le uscite del contatore vanno a tre pin di uscita digitale per indirizzare il multiplexer analogico esterno.

LUT10 decodifica il codice del contatore quando una scansione è completa e invia un impulso a Matrix0 tramite DLY8 e la porta P12. Ciò si ottiene semplicemente collegando in AND le uscite del contatore, decodificando così il numero 7 dec (0b111 binario, fine del ciclo).

Passaggio 10: configurazione del dispositivo - Logica di confronto a 3 bit

La Figura 15 mostra il circuito utilizzato per rilevare quando il loop sta iterando all'indirizzo "vincitore" corrente. In questo caso, come già discusso, un impulso digitale dovrebbe forzare un ricaricamento del risultato dell'ADC corrente per risolvere una possibile situazione di stallo.

L'indirizzo “vincitore” è memorizzato nel registro temporaneo di Matrix1 (vedi sotto), mentre l'indirizzo corrente è emesso dal contatore binario.

Le porte XNOR forniscono un'uscita vera (logica 1 o "alta") quando entrambi gli ingressi sono uguali. L'AND-ing di questo segnale per tutti i bit (LUT9) ci dà un impulso quando entrambi i codici binari sono gli stessi. I dettagli sulle porte XOR come controllore di parità possono essere trovati in Riferimento.

Il segnale "Counter-equals-Latch" viene passato a Matrix0 tramite la porta P11.

Passaggio 11: configurazione del dispositivo - Logica di confronto digitale e registro temporaneo

La parte inferiore della Figura 11 (evidenziata nella Figura 16) mostra il blocco DCMP, la parte decisionale di questo disegno.

DFF6, 7 e 8 formano un registro a 3 bit per memorizzare il numero di ingresso temporaneo "vincitore" mentre il ciclo è in esecuzione. L'ingresso ai Flip-Flop sono le uscite del contatore binario a 3 bit, come visibile nel circuito Matrix1 globale di Figura 11, qui saltato per motivi di chiarezza.

Le uscite di questo registro non possono pilotare direttamente il display a 7 segmenti perché il valore qui memorizzato cambia durante una scansione e deve essere considerato 'valido' solo al termine della scansione stessa.

Per questo motivo, le uscite del registro temporaneo si collegano al registro di loop di Matrix0 tramite le porte inter-matrix P13, P14 e P15.

È importante osservare nella Figura 16 che il registro temporaneo è temporizzato dall'uscita DCMP OUT+ quando il confronto dei registri ADC-SPI risulta in un nuovo max trovato.

Lo stesso segnale OUT+ viene passato a Matrix0, SPI CLK Logic, tramite la porta P10.

Passaggio 12: Configurazione del dispositivo - Proprietà dei componenti Matrix1

Le Figure 17-19 mostrano le finestre delle proprietà dei componenti appartenenti a Matrix1.

Passaggio 13: risultati

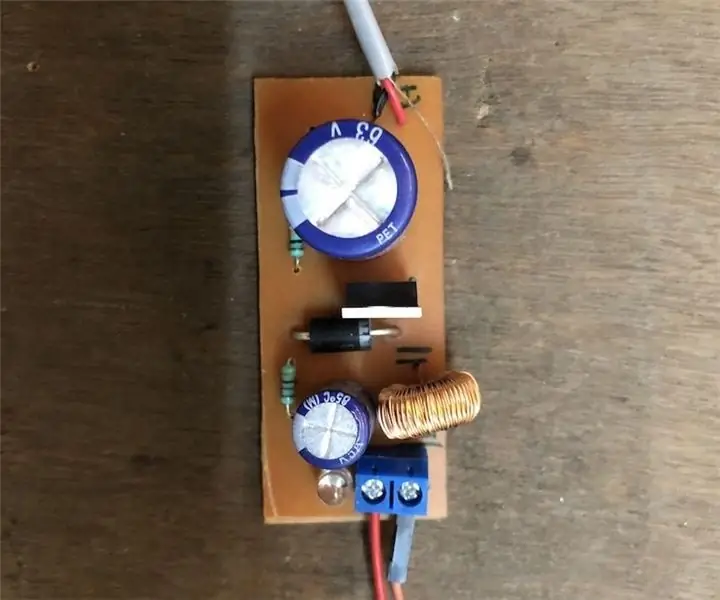

Per testare l'implementazione, è stato costruito un prototipo di scheda di valutazione, in cui le 8 tensioni di ingresso analogiche sono ottenute da una serie di divisori di resistori con TrimPots (come mostrato in Figura 20).

Il multiplexer utilizzato è un ADG508, parte che può funzionare con alimentazione singola (12 V).

Il driver del display a 7 segmenti è un 74LS47. Decodifica una parola di ingresso parallela e pilota direttamente un display a 7 segmenti ad anodo comune.

La scheda di valutazione dispone di un connettore ad angolo retto 2x10 da collegare direttamente a una piattaforma di sviluppo avanzata GreenPAK in corrispondenza del connettore di espansione, come mostrato nella Figura 21.

La combinazione con la piattaforma di sviluppo avanzata GreenPAK rende molto semplice effettuare misurazioni dei segnali per un rapido controllo. Ad esempio, la Figura 22 mostra una serie di segnali (rispettivamente CLOCK, uscita ADC INT e uscita DCMP OUT+) acquisiti da un analizzatore logico HP 54620A. Le forme d'onda vengono attivate da un fronte di salita del segnale OUT+ (sull'oscilloscopio etichettato come "A>B"), quindi questa è una cattura della forma d'onda quando viene rilevata una nuova tensione massima tra gli ingressi analogici. Infatti è stato ottenuto ruotando uno dei TrimPot della Evaluation Board per aumentare la tensione corrispondente mostrata in Figura 22.

La Figura 23 mostra lo schema della Commissione di Valutazione.

Conclusione

In questo Instructable, abbiamo implementato un rilevatore di tensione massima (o minima) a otto canali da utilizzare come aggiunta comune ai sistemi di controllo multicanale. L'approccio presentato sfrutta le caratteristiche avanzate dei componenti GreenPAK e mostra come sia possibile integrare in un unico chip funzioni analogiche e digitali. Diversi circuiti integrati commerciali possono essere sostituiti con Dialog GreenPAK in modo da ridurre le dimensioni e i costi dell'applicazione.

Consigliato:

Monitor di tensione per batterie ad alta tensione: 3 passaggi (con immagini)

Monitor di tensione per batterie ad alta tensione: in questa guida ti spiegherò come ho costruito il mio monitor di tensione della batteria per il mio longboard elettrico. Montalo come vuoi e collega solo due fili alla batteria (Gnd e Vcc). Questa guida presume che la tensione della batteria superi i 30 volt, con

Convertitore di tensione buck in modalità interruttore di riduzione della tensione CC - CC (LM2576/LM2596): 4 passaggi

Convertitore di tensione buck in modalità interruttore di riduzione della tensione CC - CC (LM2576/LM2596): Realizzare un convertitore buck altamente efficiente è un lavoro difficile e anche gli ingegneri esperti richiedono più progetti per arrivare a quello giusto. Un convertitore buck (convertitore step-down) è un convertitore di alimentazione CC-CC, che riduce la tensione (mentre aumenta

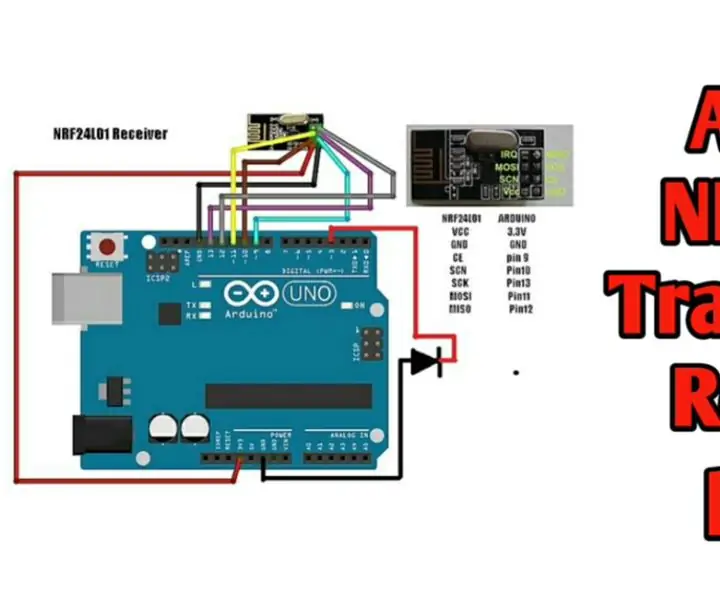

Telecomando wireless con modulo NRF24L01 da 2,4 Ghz con Arduino - Nrf24l01 Ricevitore trasmettitore 4 canali / 6 canali per quadricottero - Elicottero Rc - Aereo RC con Arduino: 5

Telecomando wireless con modulo NRF24L01 da 2,4 Ghz con Arduino | Nrf24l01 Ricevitore trasmettitore 4 canali / 6 canali per quadricottero | Elicottero Rc | Aereo radiocomandato con Arduino: per far funzionare un'auto radiocomandata | Quadricottero | Drone | Aereo RC | Barca RC, abbiamo sempre bisogno di un ricevitore e trasmettitore, supponiamo che per RC QUADCOPTER abbiamo bisogno di un trasmettitore e ricevitore a 6 canali e quel tipo di TX e RX è troppo costoso, quindi ne faremo uno sul nostro

Antenna da Interno BIQUAD, in Rame e Legno per la Ricezione di Canali HDTV in Banda UHF (CANALI 14-51): 7 Passi

Antenna da Interno BIQUAD, Realizzata in Rame e Legno per la Ricezione di Canali HDTV in Banda UHF (CANALI 14-51): In commercio esistono svariate antenne per la televisione. I più popolari secondo i miei criteri sono: UDA-YAGIS, Dipolo, Dipolo con riflettori, Antenne Patch e Logaritmiche. A seconda delle condizioni, la distanza dalla trasmissione a

Amplificatore analogico a 8 canali per PC o HomeTheater: 12 passaggi (con immagini)

Amplificatore analogico a 8 canali per PC o HomeTheater: questo è il mio primo istruibile. Ti insegnerò come realizzare un amplificatore a 8 canali per un computer o un sistema audio con uscite analogiche separate, l'ho usato per il mio computer desktop, per guardare film, ascoltare musica in HD e giocare, inoltre