Sommario:

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:02.

- Ultima modifica 2025-01-23 14:49.

Analizzerò come affronta la sfida del design dell'alimentatore DC-DC Technologies.

I progettisti di sistemi di alimentazione devono affrontare una pressione costante da parte del mercato per trovare modi per sfruttare al meglio la potenza disponibile. Nei dispositivi portatili, una maggiore efficienza prolunga la durata della batteria e aggiunge più funzionalità in confezioni più piccole. Nei server e nelle stazioni base, i guadagni di efficienza possono far risparmiare direttamente l'infrastruttura (sistemi di raffreddamento) e i costi operativi (bollette elettriche). Per soddisfare le richieste del mercato, i progettisti di sistemi stanno migliorando i processi di conversione di potenza in più aree, comprese topologie di commutazione più efficienti, innovazioni di package e nuovi dispositivi a semiconduttore basati su carburo di silicio (SiC) e nitruro di gallio (GaN).

Passaggio 1: miglioramento della topologia del convertitore di commutazione

Per sfruttare appieno la potenza disponibile, le persone stanno adottando sempre più progetti basati sulla tecnologia di commutazione piuttosto che sulla tecnologia lineare. L'alimentatore switching (SMPS) ha una potenza effettiva superiore al 90%. Ciò estende la durata della batteria dei sistemi portatili, riduce il costo dell'elettricità per le apparecchiature di grandi dimensioni e consente di risparmiare lo spazio precedentemente utilizzato per i componenti del dissipatore di calore.

Il passaggio a una topologia commutata presenta alcuni inconvenienti e il suo design più complesso richiede ai progettisti di disporre di più competenze. I progettisti devono avere familiarità con le tecnologie analogiche e digitali, l'elettromagnetismo e il controllo a circuito chiuso. I progettisti di circuiti stampati (PCB) devono prestare maggiore attenzione alle interferenze elettromagnetiche (EMI) perché le forme d'onda di commutazione ad alta frequenza possono causare problemi nei circuiti analogici e RF sensibili.

Prima dell'invenzione del transistor, è stato proposto il concetto di base della conversione di potenza in modalità commutata: ad esempio, il sistema di scarica induttiva di tipo Kate inventato nel 1910, che utilizzava un vibratore meccanico per implementare un convertitore boost flyback per un sistema di accensione automobilistico.

La maggior parte delle topologie standard esiste da decenni, ma ciò non significa che gli ingegneri non adattino i progetti standard per accogliere nuove applicazioni, in particolare i circuiti di controllo. L'architettura standard utilizza una frequenza fissa per mantenere una tensione di uscita costante reimmettendo parte della tensione di uscita (controllo della modalità di tensione) o controllando la corrente indotta (controllo della modalità di corrente) in diverse condizioni di carico. I designer migliorano costantemente per superare i difetti del design di base.

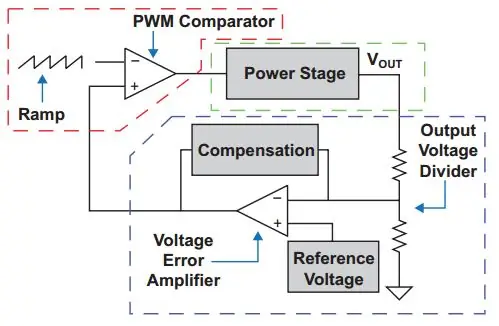

La Figura 1 è uno schema a blocchi di un sistema di controllo della modalità di tensione ad anello chiuso (VMC) di base. Lo stadio di potenza è costituito da un interruttore di alimentazione e da un filtro di uscita. Il blocco di compensazione include un partitore di tensione di uscita, un amplificatore di errore, una tensione di riferimento e un componente di compensazione dell'anello. Un modulatore di larghezza di impulso (PWM) utilizza un comparatore per confrontare il segnale di errore con un segnale a rampa fissa per produrre una sequenza di impulsi di uscita proporzionale al segnale di errore.

Sebbene i diversi carichi del sistema VMC abbiano regole di uscita rigide e siano facili da sincronizzare con il clock esterno, l'architettura standard presenta alcuni inconvenienti. La compensazione dell'anello riduce la larghezza di banda dell'anello di controllo e rallenta la risposta ai transitori; l'amplificatore di errore aumenta la corrente di funzionamento e riduce l'efficienza.

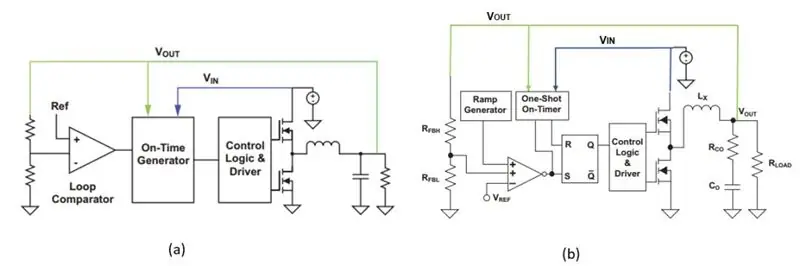

Lo schema di controllo del tempo di accensione costante (COT) fornisce buone prestazioni transitorie senza compensazione del circuito. Il controllo COT utilizza un comparatore per confrontare la tensione di uscita regolata con la tensione di riferimento: quando la tensione di uscita è inferiore alla tensione di riferimento, viene generato un impulso di tempo fisso. A bassi cicli di lavoro, questo fa sì che la frequenza di commutazione sia molto alta, quindi il controller COT adattivo genera un tempo di attivazione che varia con le tensioni di ingresso e di uscita, che mantiene la frequenza quasi costante allo stato stazionario. La topologia D-CAP di Texas Instrument rappresenta un miglioramento rispetto all'approccio COT adattivo: il controller D-CAP aggiunge una tensione di rampa all'ingresso del comparatore di feedback, che migliora le prestazioni del jitter riducendo la banda di rumore nell'applicazione. La Figura 2 è un confronto tra i sistemi COT e D-CAP.

Figura 2: Confronto tra topologia COT standard (a) e topologia D-CAP (b) (Fonte: Texas Instruments) Esistono diverse varianti della topologia D-CAP per esigenze diverse. Ad esempio, il controller PWM a mezzo ponte TPS53632 utilizza l'architettura D-CAP+, utilizzata principalmente in applicazioni ad alta corrente e può pilotare livelli di potenza fino a 1 MHz in convertitori POL da 48 V a 1 V con efficienze fino al 92%.

A differenza di D-CAP, il circuito di feedback D-CAP+ aggiunge un componente proporzionale alla corrente indotta per un controllo preciso della caduta. L'amplificatore di errore aumentato migliora la precisione del carico CC in una varietà di condizioni di linea e di carico.

La tensione di uscita del controller è impostata dal DAC interno. Questo ciclo inizia quando la retroazione di corrente raggiunge il livello di tensione di errore. Questa tensione di errore corrisponde alla differenza di tensione amplificata tra la tensione di setpoint del DAC e la tensione di uscita di retroazione.

Passaggio 2: migliorare le prestazioni in condizioni di carico leggero

Per i dispositivi portatili e indossabili, è necessario migliorare le prestazioni in condizioni di carico leggero per prolungare la durata della batteria. Molte applicazioni portatili e indossabili sono per la maggior parte del tempo in modalità standby "sospensione temporanea" o "sleep" a bassa potenza, attivate solo in risposta all'input dell'utente o misurazioni periodiche, quindi ridurre al minimo il consumo energetico in modalità standby. È la priorità assoluta.

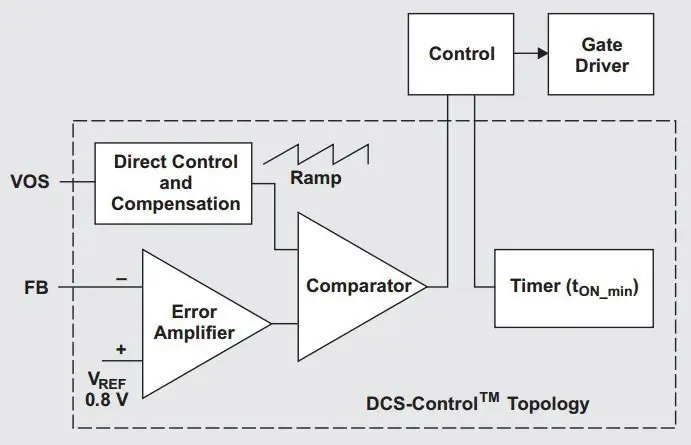

La topologia DCS-ControlTM (Direct Control to Seamless Transition to Energy Saver Mode) combina i vantaggi di tre diversi schemi di controllo (vale a dire, modalità isteresi, modalità tensione e modalità corrente) per migliorare le prestazioni in condizioni di carico leggero, in particolare la transizione a O quando lasciando lo stato di carico leggero. Questa topologia supporta le modalità PWM per carichi medi e pesanti, nonché la modalità di risparmio energetico (PSM) per carichi leggeri.

Durante il funzionamento PWM, il sistema funziona alla sua frequenza di commutazione nominale basata sulla tensione di ingresso e controlla la variazione di frequenza. Se la corrente di carico diminuisce, il convertitore passa al PSM per mantenere un'elevata efficienza fino a quando non scende a un carico molto leggero. A PSM, la frequenza di commutazione diminuisce linearmente con la corrente di carico. Entrambe le modalità sono controllate da un singolo blocco di controllo, quindi la transizione da PWM a PSM è perfetta e non influisce sulla tensione di uscita.

La Figura 3 è uno schema a blocchi del DCS-ControlTM. Il circuito di controllo acquisisce informazioni sulla variazione della tensione di uscita e le invia direttamente al comparatore veloce. Il comparatore imposta la frequenza di commutazione (come costante per condizioni operative stazionarie) e fornisce una risposta immediata alle variazioni dinamiche del carico. Il circuito di retroazione della tensione regola accuratamente il carico CC. La rete di regolazione con compensazione interna consente un funzionamento rapido e stabile con piccoli componenti esterni e condensatori a bassa ESR.

Figura 3: Implementazione della topologia DCS-ControlTM nel convertitore buck TPS62130 (Fonte: Texas Instruments)

Il convertitore di potenza a commutazione sincrono TPS6213xA-Q1 si basa sulla topologia DCS-ControlTM ed è ottimizzato per applicazioni POL ad alta densità di potenza. La tipica frequenza di commutazione di 2,5 MHz consente l'uso di piccoli induttori e fornisce una risposta rapida ai transitori e un'elevata precisione della tensione di uscita. Il TPS6213 funziona da un intervallo di tensione di ingresso da 3V a 17V e può fornire fino a 3A di corrente continua tra 0,9V e tensioni di uscita 6V.

Consigliato:

Recupero degli alimentatori del vecchio PC: 12 passaggi (con immagini)

Recupero di vecchi alimentatori per PC: dagli anni '90, il mondo è stato invaso dai PC. La situazione continua fino ad oggi. I computer più vecchi, fino al 2014… 2015, sono in gran parte fuori uso. Poiché ogni PC ha un alimentatore, ce ne sono un gran numero abbandonati sotto forma di rifiuti

Fai in modo che il tuo computer dica ciò che scrivi usando il Blocco note: 3 passaggi

Fai in modo che il tuo computer dica ciò che scrivi usando il Blocco note: ecco un codice interessante creato da noi per far parlare il tuo computer ciò che scrivi. Useremo il blocco note per crearlo. Iniziamo

Utilizzo della corrente alternata con i LED (parte 4) - le nuove tecnologie: 6 passaggi (con immagini)

Utilizzo della corrente alternata con i LED (Parte 4) - le nuove tecnologie: alcuni dei blocchi stradali nell'accettazione generale dei LED in casa sono stati il costo relativamente elevato per lumen ei sistemi di conversione dell'energia complicati e goffi. Negli ultimi mesi, una serie di nuovi sviluppi promette di avvicinarci di un passo a

Come creare un'unità flash che copia i file degli utenti in modo silenzioso e automatico: 7 passaggi

Come creare un'unità flash che copia i file degli utenti in modo silenzioso e automatico: ****** QUESTO ISTRUZIONI È SOLO A SCOPO INFORMATIVO È ILLEGALE COPIARE I FILE DI QUALCUNO SENZA IL LORO PERMESSO NON SONO RESPONSABILE DI QUALSIASI COSA CHE PU O NON PU ACCADERE SE QUESTO LE INFORMAZIONI SONO UTILIZZATE IN MODO IMPROPRIO **************** Come costruire un

Come fare in modo che il tuo laptop risparmi la carica della batteria con una perdita minima di prestazioni: 4 passaggi

Come far risparmiare al tuo laptop la carica della batteria con una minima perdita di prestazioni: chi dice che il tuo laptop deve subire prestazioni lente per risparmiare un po' di energia? La variazione delle prestazioni o della durata della batteria dipende dall'età del laptop, dall'età della batteria e da altri programmi e impostazioni. Ecco alcuni semplici passaggi per aiutare ad aumentare