Sommario:

- Passaggio 1: aggiungi sorgenti e scegli "Aggiungi o crea sorgenti di simulazione

- Passaggio 2: crea un file chiamato Enable_sr_tb

- Passaggio 3: creare un file del banco di prova

- Passaggio 4: impostare Enable_sr_tb come livello superiore sotto la simulazione

- Passaggio 5: eseguire la sintesi e la simulazione comportamentale

- Passaggio 6: valutare il risultato della simulazione

- Autore John Day day@howwhatproduce.com.

- Public 2024-01-30 10:04.

- Ultima modifica 2025-01-23 14:49.

Ho realizzato questo progetto di simulazione per una lezione online. Il progetto è scritto da Verilog. Useremo la simulazione in Vivado per visualizzare la forma d'onda in enable_sr(enable digit) dal progetto di cronometro precedentemente creato. Inoltre, utilizzeremo l'attività di sistema per visualizzare gli errori da noi commessi nella progettazione.

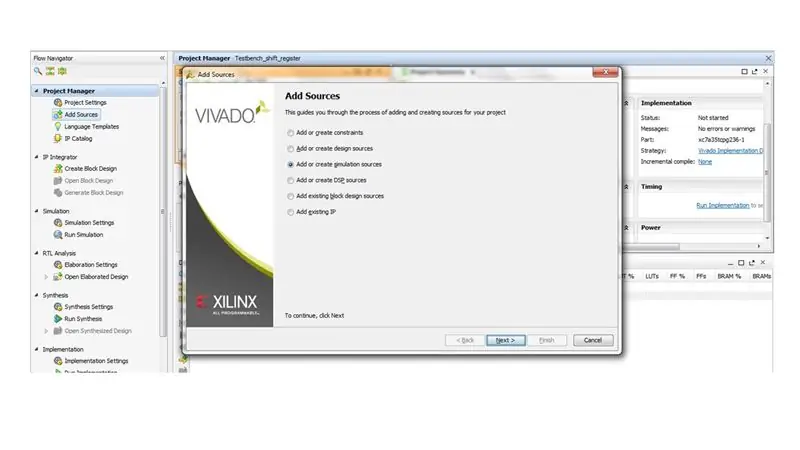

Passaggio 1: aggiungi sorgenti e scegli "Aggiungi o crea sorgenti di simulazione

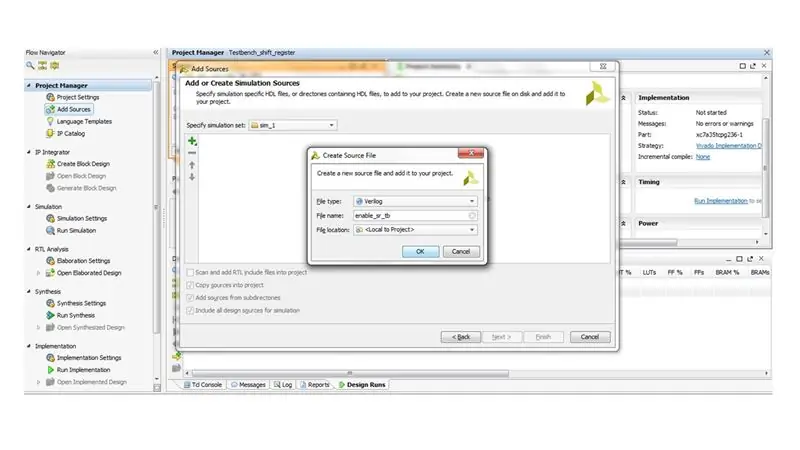

Passaggio 2: crea un file chiamato Enable_sr_tb

Passaggio 3: creare un file del banco di prova

1. Importare il modulo enable_sr dal progetto cronometro. Questo è il file che vogliamo simulare

2. Creare il modulo banco di prova enable_sr_tb();

3. Digitare gli ingressi e le uscite del modulo enable_sr(). Ricorda che gli ingressi per enable_sr ora sono di tipo register mentre le uscite diventano di tipo net.

4. Istanziare l'unità in prova (uut) che è enable_sr

5. Genera un orologio il cui periodo (T) è 20ns

6. Utilizzare l'istruzione condizionale per creare un sistema di controllo degli errori. In questo esempio, vogliamo verificare se sono attive più di una cifra.

Nota: nel file enable_sr() originale, dovremmo inizializzare il pattern come 4'b0011 in modo che ci siano due cifre attive per creare un errore

7. Usa l'attività di sistema $display per mostrare l'errore

8. Utilizzare l'attività di sistema $finish per completare la simulazione al tempo 400ns

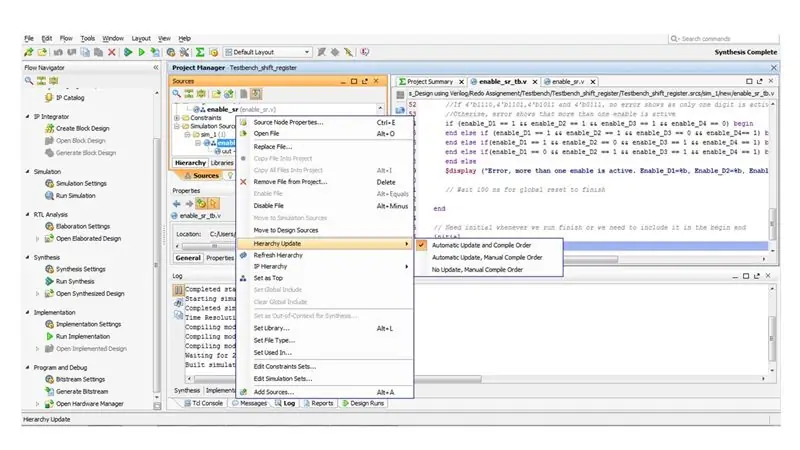

Passaggio 4: impostare Enable_sr_tb come livello superiore sotto la simulazione

Passaggio 5: eseguire la sintesi e la simulazione comportamentale

- Prima di eseguire la simulazione comportamentale, esegui la sintesi per assicurarti che non ci siano errori di sintassi nel file testbench e nell'unità sotto il file di test

- Esegui la simulazione comportamentale

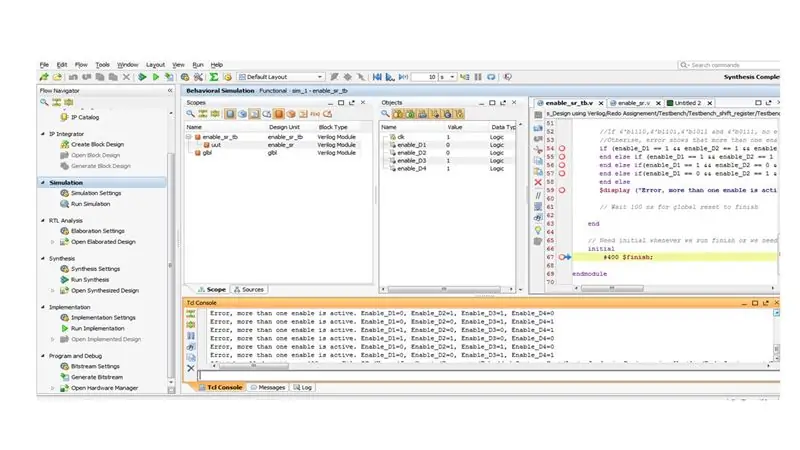

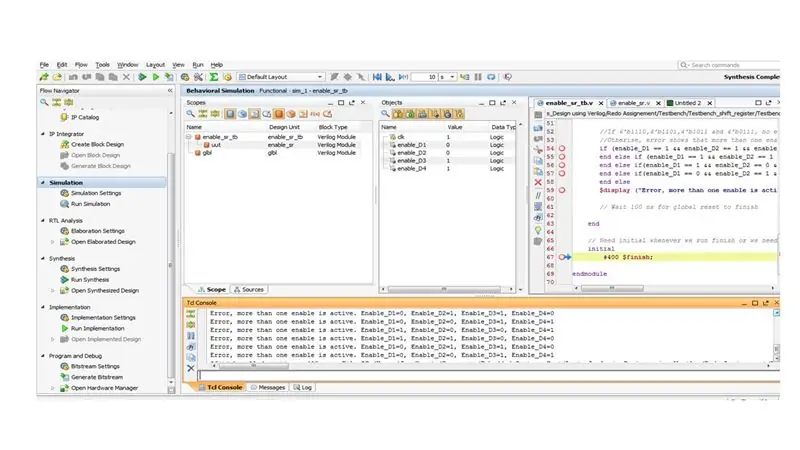

Passaggio 6: valutare il risultato della simulazione

Vedrai le finestre di simulazione. Contiene diversi pannelli.

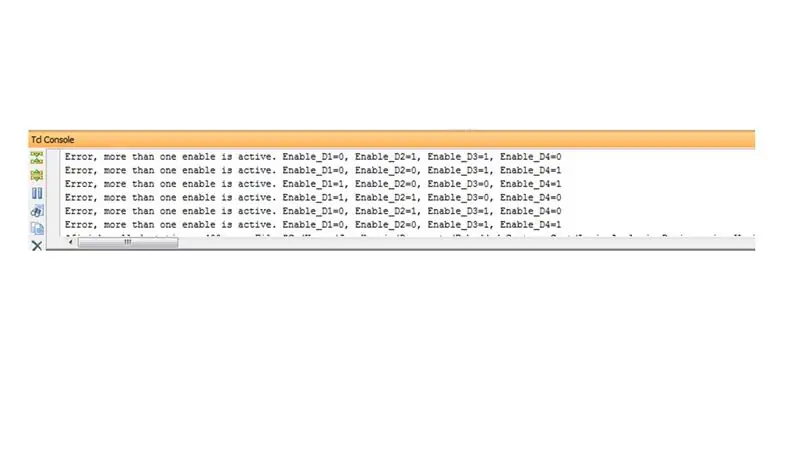

Vedrai il messaggio di errore nel pannello della console. Questo mostra che più di una cifra è attiva durante il periodo di simulazione.

Puoi anche vedere la forma d'onda nell'oscilloscopio

In allegato il file del progetto.

Consigliato:

Come creare un registratore di dati in tempo reale di umidità e temperatura con Arduino UNO e SD-Card - Simulazione del data logger DHT11 in Proteus: 5 passaggi

Come creare un registratore di dati in tempo reale di umidità e temperatura con Arduino UNO e SD-Card | Simulazione DHT11 Data-logger in Proteus: Introduzione: ciao, sono Liono Maker, ecco il link YouTube. Stiamo realizzando un progetto creativo con Arduino e lavoriamo su sistemi embedded.Data-Logger: Un data logger (anche data-logger o data recorder) è un dispositivo elettronico che registra i dati nel tempo w

Come Usare un Telefono Android come Webcam con Skype: 5 Passaggi

Come utilizzare un telefono Android come webcam con Skype: C'è un vecchio detto che un'immagine vale più di mille parole… e c'è un nuovo detto che un video vale un milione. Ora potrebbe sembrare un'esagerazione, ma c'è un'enorme differenza tra parlare a qualcuno durante una chiamata e parlare a

Visuino Come usare un pulsante come ingresso per controllare cose come il LED: 6 passaggi

Visuino Come utilizzare un pulsante come input per controllare cose come il LED: In questo tutorial impareremo come accendere e spegnere il LED utilizzando un semplice pulsante e Visuino. Guarda un video dimostrativo

Come usare il Wiimote come mouse del computer usando le candele come sensore!!: 3 passaggi

Come utilizzare il Wiimote come mouse del computer utilizzando le candele come sensore!!: questa guida ti mostrerà come collegare il telecomando Wii (Wiimote) al PC e utilizzarlo come mouse

Come Usare una TV come Monitor di Computer: 6 Passaggi

Come usare una TV come monitor di un computer: va bene così.. Questo è il mio primo istruttore, quindi abbi pazienza con me… In questo tutorial ti mostrerò.. è giusto.. come usare una TV come monitor di un computer ! Funziona abbastanza bene, ma ci sono dei limiti… per esempio non puoi leggere un testo piccolo, ma un pi